Altera Low Latency Ethernet 10G MAC User Manual

Page 60

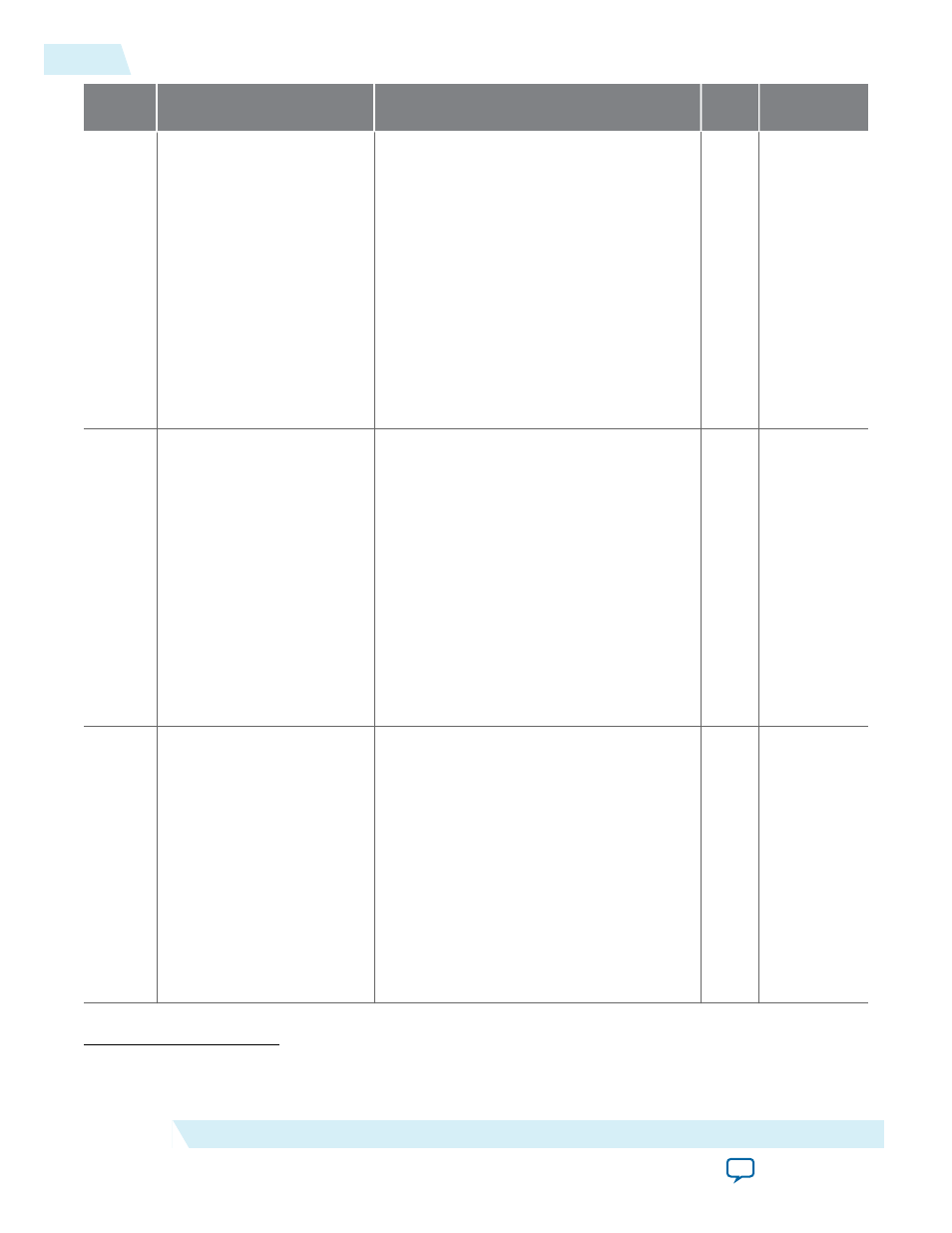

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x0028

tx_preamble_control

(4)

• Bit 0—configures the preamble

passthrough mode on transmit.

0: Disables preamble passthrough. The

MAC IP core inserts the standard

preamble specified by the IEEE 802.3

specifications into the data frame.

1: Enables preamble passthrough. The

MAC IP core identifies the first 8 bytes of

the data frame from the client as a custom

preamble.

• Bits 31:1—reserved.

Configure this register before you enable the

MAC IP core for operations.

RW

0x0

0x002A

tx_src_addr_override

• Bit 0—configures source address override.

0: Disables source address override. The

client must fill the source address field

with a valid address..

1: Enables source address override. The

MAC IP core overwrites the source

address field in data frames with the

primary MAC address specified in the

tx_

primary_mac_addr0

and

tx_primary_

mac_addr1

registers.

• Bits 31:1—reserved.

Configure this register before you enable the

MAC IP core for operations.

RW

0x0

0x002C

tx_frame_maxlength

• Bits 15:0—specify the maximum allowable

frame length. The MAC IP core uses this

register only for the purpose of collecting

statistics. When the length of the data

frame from the client exceeds this value,

the MAC IP core asserts the

avalon_st_

txstatus_error[1]

signal to flag the

frame as oversized. The MAC IP core then

forwards the oversized frame through the

transmit datapath as is.

• Bits 31:16—reserved.

Configure this register before you enable the

MAC IP core for operations.

RW

0x5EE (1518)

(4)

This register is used only when you turn on Enable preamble pass-through mode option. It is reserved

when not used.

4-8

TX_Configuration and Status Registers

UG-01144

2014.12.15

Altera Corporation

Configuration Registers for LL Ethernet 10G MAC