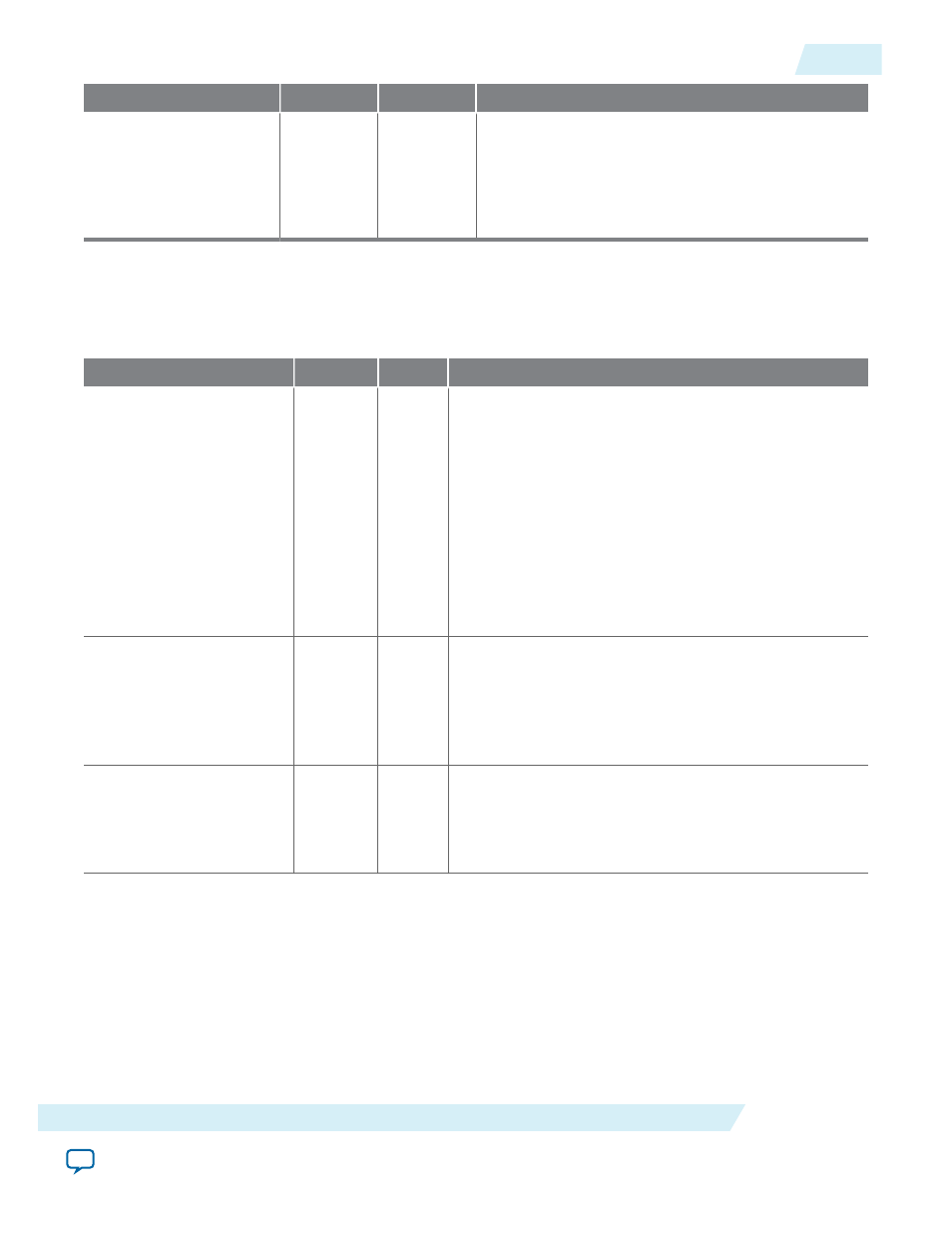

Avalon-st flow control signals, Avalon-st flow control signals -7 – Altera Low Latency Ethernet 10G MAC User Manual

Page 89

Signal

Direction

Width

Description

avalon_st_rx_

empty[]

Out

2/3

Contains the number of empty bytes during the

cycle that contain the end of the RX data.

The width is 3 bits when you enable the Use 64-bit

Ethernet 10G MAC Avalon Streaming Interface

option. Otherwise, it is 2 bits.

Avalon-ST Flow Control Signals

Table 5-8: Avalon-ST Flow Control Signals

Signal

Direction

Width

Description

avalon_st_pause_

data[]

In

2

Set this signal to the following values to trigger the

corresponding actions.

• 0x0: Stops pause frame generation.

• 0x1: Generates an XON pause frame.

• 0x2: Generates an XOFF pause frame. The MAC IP

core sets the pause quanta field in the pause frame to

the value in the

tx_pauseframe_quanta

register.

• 0x3: Reserved.

Note: This signal only takes effect if

tx_

pauseframe_enable[2:1]

is 00 (default)

avalon_st_tx_pause_

length_valid

In

1

This signal is present in the MAC TX only variation.

Assert this signal to request the MAC IP core to suspend

data transmission. When you assert this signal, ensure

that a valid pause quanta is available on the

avalon_st_

tx_pause_length_data

bus.

avalon_st_tx_pause_

length_data[]

In

16

This signal is present only in the MAC TX only

variation.

Use this bus to specify the pause quanta in unit of

quanta, where 1 unit = 512 bits time.

UG-01144

2014.12.15

Avalon-ST Flow Control Signals

5-7

Interface Signals for LL Ethernet 10G MAC

Altera Corporation