Altera Low Latency Ethernet 10G MAC User Manual

Page 66

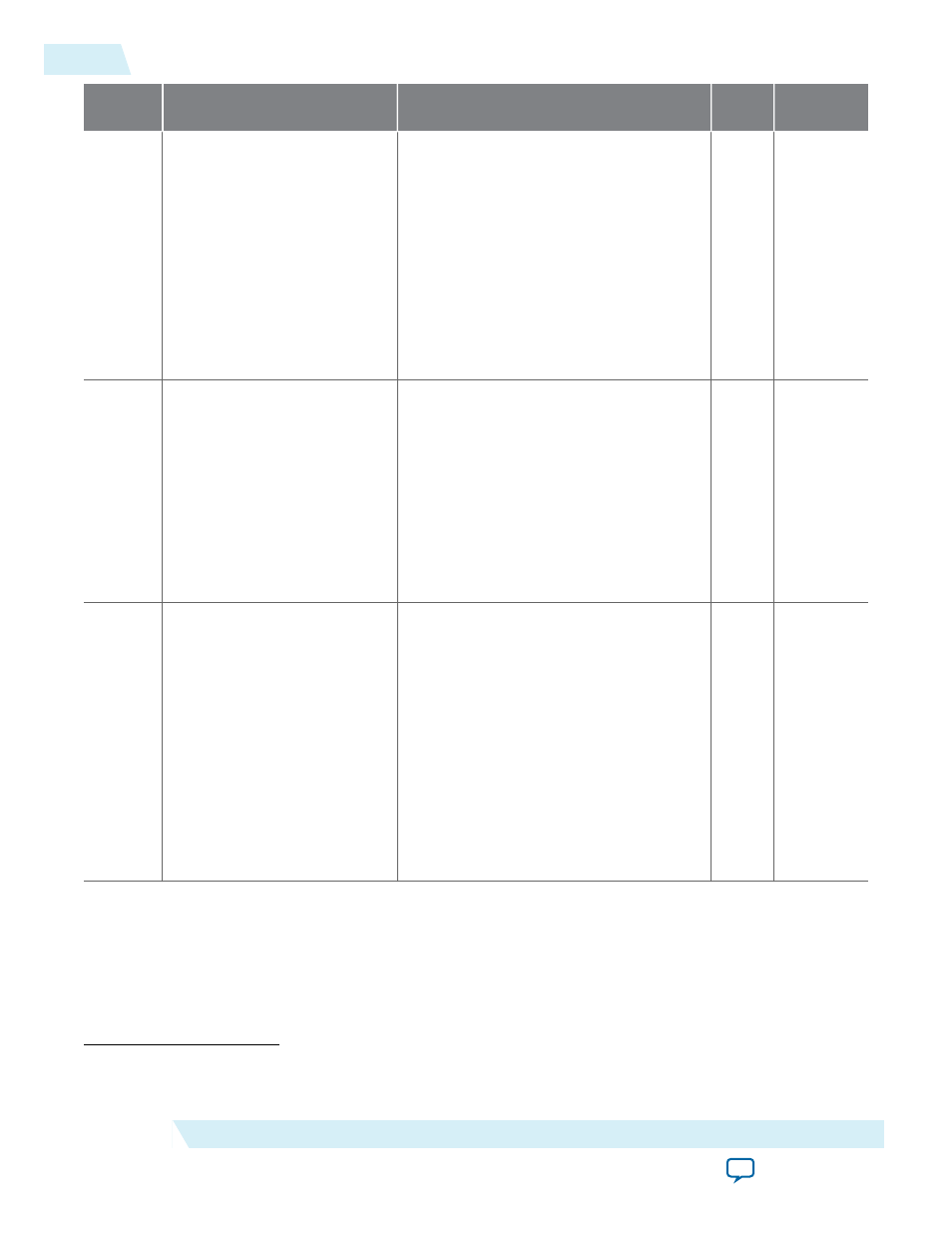

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x00A6

rx_crccheck_control

CRC checking on receive.

• Bit 0—always set this bit to 0.

• Bit 1—CRC checking enable.

0: Ignores the CRC field.

1: Checks the CRC field and reports the

status to

avalon_st_rx_error[1]

and

avalon_st_rxstatus_error

.

• Bits 31:2—reserved.

Configure this register before you enable

the MAC IP core for operations.

RW

0x2

0x00A8

rx_custom_preamble_forward

(7)

• Bit 0—configures the forwarding of the

custom preamble to the client.

0: Removes the custom preamble from

the RX frame.

1: Retains and forwards the custom

preamble to the client.

• Bits 31:1—reserved.

Configure this register before you enable

the MAC IP core for operations.

RW

0x0

0x00AA

rx_preamble_control

(7)

• Bit 0—preamble passthrough enable on

receive.

0: Disables preamble passthrough. The

MAC IP core checks for START and

SFD during packet decapsulation

process.

1: Enables preamble passthrough. The

MAC IP core checks only for START

during packet decapsulation process.

• Bits 31:1—reserved.

Configure this register before you enable

the MAC IP core for operations.

RW

0x0

(7)

This register is used only when you turn on the Enable preamble pass-through mode option. It is reserved

when not used.

4-14

RX Configuration and Status Registers

UG-01144

2014.12.15

Altera Corporation

Configuration Registers for LL Ethernet 10G MAC