Gmii tx signals, Gmii tx signals -16 – Altera Low Latency Ethernet 10G MAC User Manual

Page 98

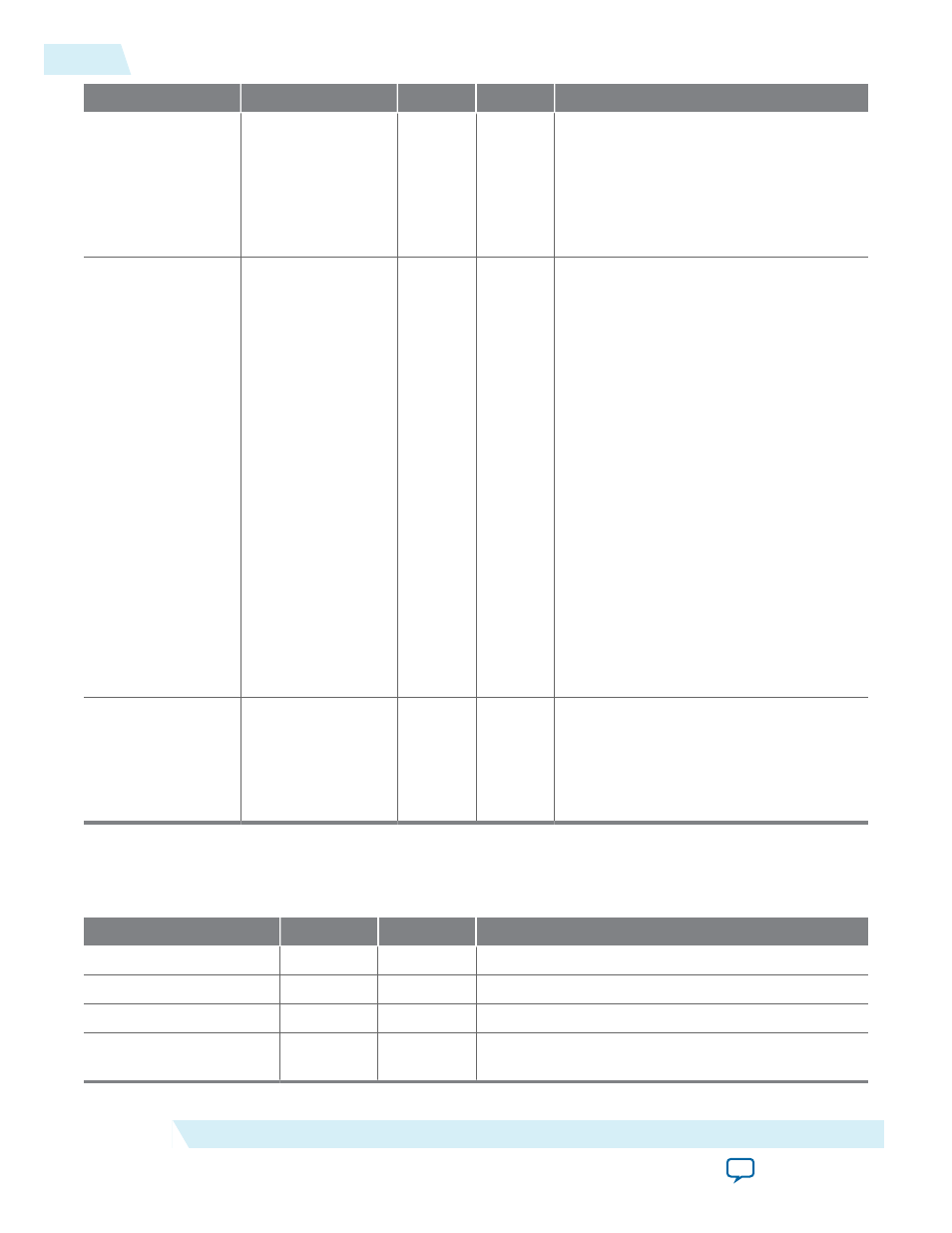

Signal

Condition

Direction

Width

Description

xgmii_rx_valid

Use legacy Ethernet

10G MAC XGMII

interface disabled.

Enable 10GBASE-R

register mode

enabled.

In

1

When asserted, indicates that the data

and control buses are valid.

xgmii_rx[]

Use legacy Ethernet

10G MAC XGMII

interface enabled.

In

72

8-lane SDR XGMII receive data and

control bus. Each lane contains 8 data

plus 1 control bits. The signal mapping

is compatible with the 64-bit MAC.

• Lane 0 data:

xgmii_rx[7:0]

• Lane 0 control:

xgmii_rx[8]

• Lane 1 data:

xgmii_rx[16:9]

• Lane 1 control:

xgmii_rx[17]

• Lane 2 data:

xgmii_rx[25:18]

• Lane 2 control:

xgmii_rx[26]

• Lane 3 data:

xgmii_rx[34:27]

• Lane 3 control:

xgmii_rx[35]

• Lane 4 data:

xgmii_rx[43:36]

• Lane 4 control:

xgmii_rx[44]

• Lane 5 data:

xgmii_rx[52:45]

• Lane 5 control:

xgmii_rx[53]

• Lane 6 data:

xgmii_rx[61:54]

• Lane 6 control:

xgmii_rx[62]

• Lane 7 data:

xgmii_rx[70:63]

• Lane 7 control:

xgmii_rx[71]

link_fault_

status_xgmii_

rx_data[]

—

Out

2

The following values indicate the link

fault status:

• 0x0 = No link fault

• 0x1 = Local fault

• 0x2 = Remote fault

GMII TX Signals

Table 5-13: GMII TX Signals

Signal

Direction

Width

Description

gmii_tx_clk

In

1

125-MHz TX clock.

gmii_tx_d []

Out

8

TX data.

gmii_tx_en

Out

2

When asserted, indicates the TX data is valid.

gmii_tx_err

Out

2

When asserted, indicates the TX data contains

error.

5-16

GMII TX Signals

UG-01144

2014.12.15

Altera Corporation

Interface Signals for LL Ethernet 10G MAC