Altera Low Latency Ethernet 10G MAC User Manual

Page 68

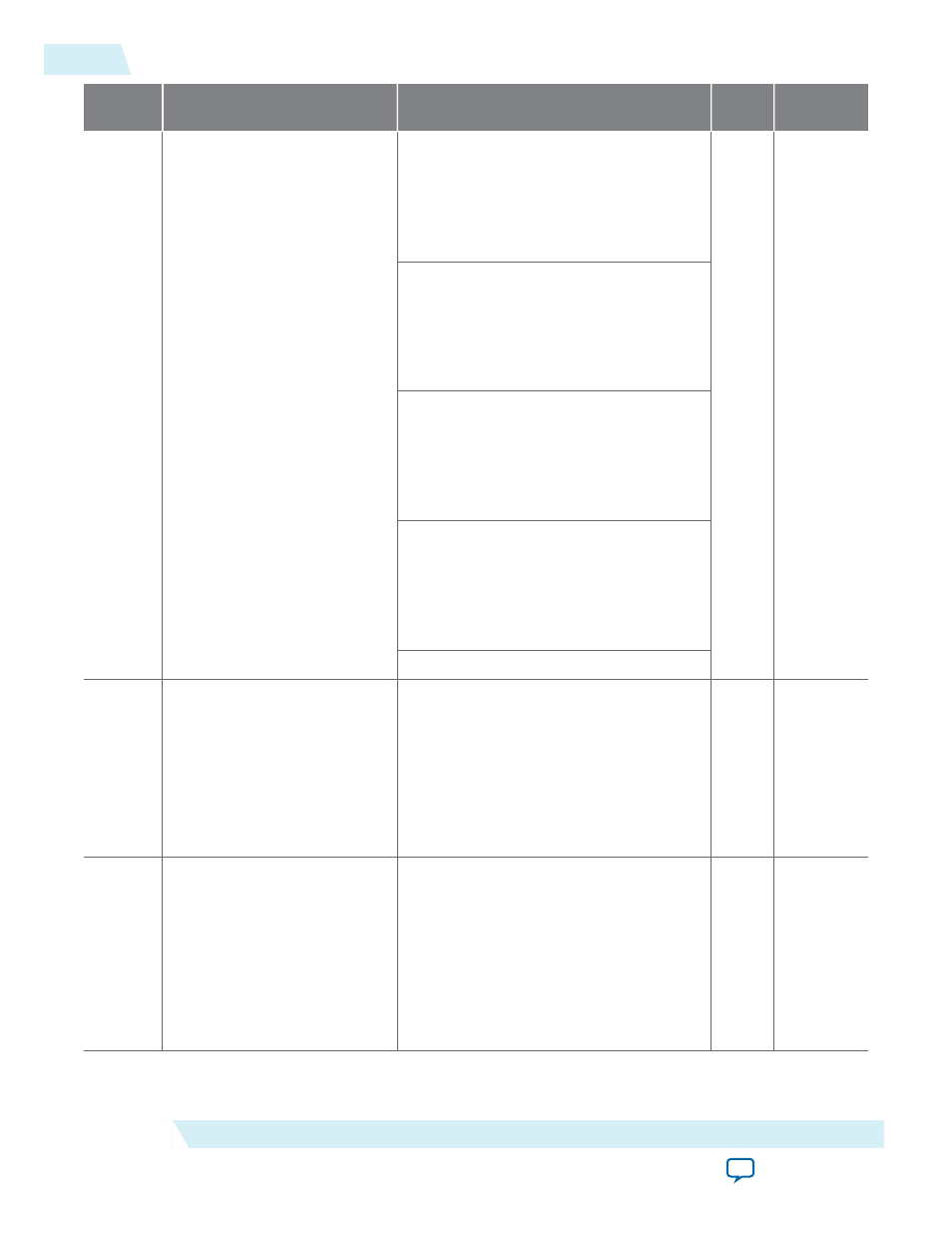

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x00AC

rx_frame_control

Bit 16—

EN_SUPP0

0: Disables the use of supplementary

address 0.

1: Enables the use of supplementary address

0.

RW

0x3

Bit 17—

EN_SUPP1

0: Disables the use of supplementary address

1.

1: Enables the use of supplementary address

1.

Bit 18—

EN_SUPP2

0: Disables the use of supplementary address

2.

1: Enables the use of supplementary address

2.

Bit 19—

EN_SUPP3

0: Disables the use of supplementary address

3.

1: Enables the use of supplementary address

3.

Bits 31:20—reserved.

0x00AE

rx_frame_maxlength

• Bits 15:0—specify the maximum

allowable frame length. The MAC

asserts the

avalon_st_rx_error[3]

signal when the length of the RX frame

exceeds the value of this register.

• Bits 16:31—reserved.

Configure this register before you enable

the MAC IP core for operations.

RW

1518

0x00AF

rx_vlan_detection

• Bit 0—RX VLAN detection disable.

0: The MAC detects VLAN and stacked

VLAN frames.

1: The MAC does not detect VLAN and

stacked VLAN frames. When received,

the MAC treats them as basic frames and

considers their tags as payload bytes.

• Bits 31:1—reserved.

RW

0x0

4-16

RX Configuration and Status Registers

UG-01144

2014.12.15

Altera Corporation

Configuration Registers for LL Ethernet 10G MAC