Xgmii encapsulation, Xgmii encapsulation -6 – Altera Low Latency Ethernet 10G MAC User Manual

Page 28

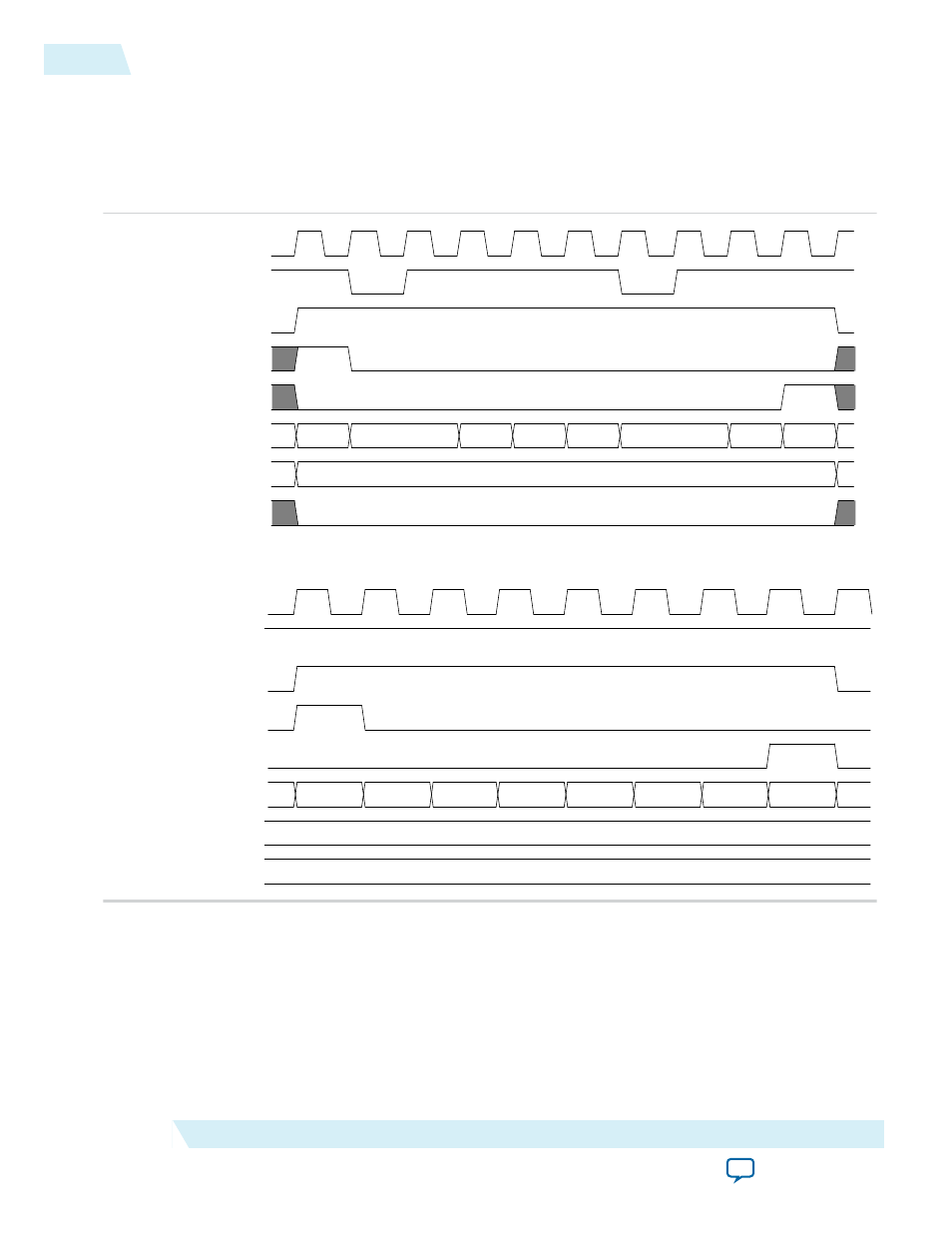

The following figure shows the timing diagram on the Avalon-ST data interfaces where CRC insertion is

disabled on transmit and CRC removal is disabled on receive. The MAC TX receives the frame from the

client with a CRC-32 checksum (4EB00AF4). The frame with the same CRC-32 checksum is then looped

back to the RX datapath.

Figure 3-5: Avalon-ST TX and RX Interface with CRC Insertion Disabled

tx_312_5_clk

avalon_st_tx_ready

avalon_st_tx_valid

avalon_st_tx_startofpacket

avalon_st_tx_endofpacket

avalon_st_tx_data[31:0]

avalon_st_tx_empty[1:0]

avalon_st_tx_error

0

rx_312_5_clk

avalon_st_rx_ready

avalon_st_rx_valid

avalon_st_rx_startofpacket

avalon_st_rx_endofpacket

avalon_st_rx_data[31:0]

avalon_st_rx_empty[1:0]

avalon_st_rx_error[5:0]

...4EB30AF4

...4EB30AF4

0

XGMII Encapsulation

By default, the MAC TX inserts 7-byte preamble, 1-byte SFD and 1-byte EFD (0xFD) into frames received

from the client.

The MAC TX also supports custom preamble in 10G operations. To use custom preamble, set the

tx_preamble_control

register to 1. In this mode, the MAC TX accepts the first 8 bytes in the frame from

the client as custom preamble and inserts only 1-byte EFD (0xFD) into the frame. The MAC TX also

replaces the first byte of the preamble with 1-byte START (0xFB).

3-6

XGMII Encapsulation

UG-01144

2014.12.15

Altera Corporation

Functional Description of LL Ethernet 10G MAC