Primary mac address, Mac reset control register, Primary mac address -5 – Altera Low Latency Ethernet 10G MAC User Manual

Page 57: Mac reset control register -5

Access

Definition

RW1C

Read and write 1 to clear. Writing 0 has no effect. Writing 1 clears the bit if the bit has

been set to 1 by the IP core. The client takes precedence over the IP core.

Primary MAC Address

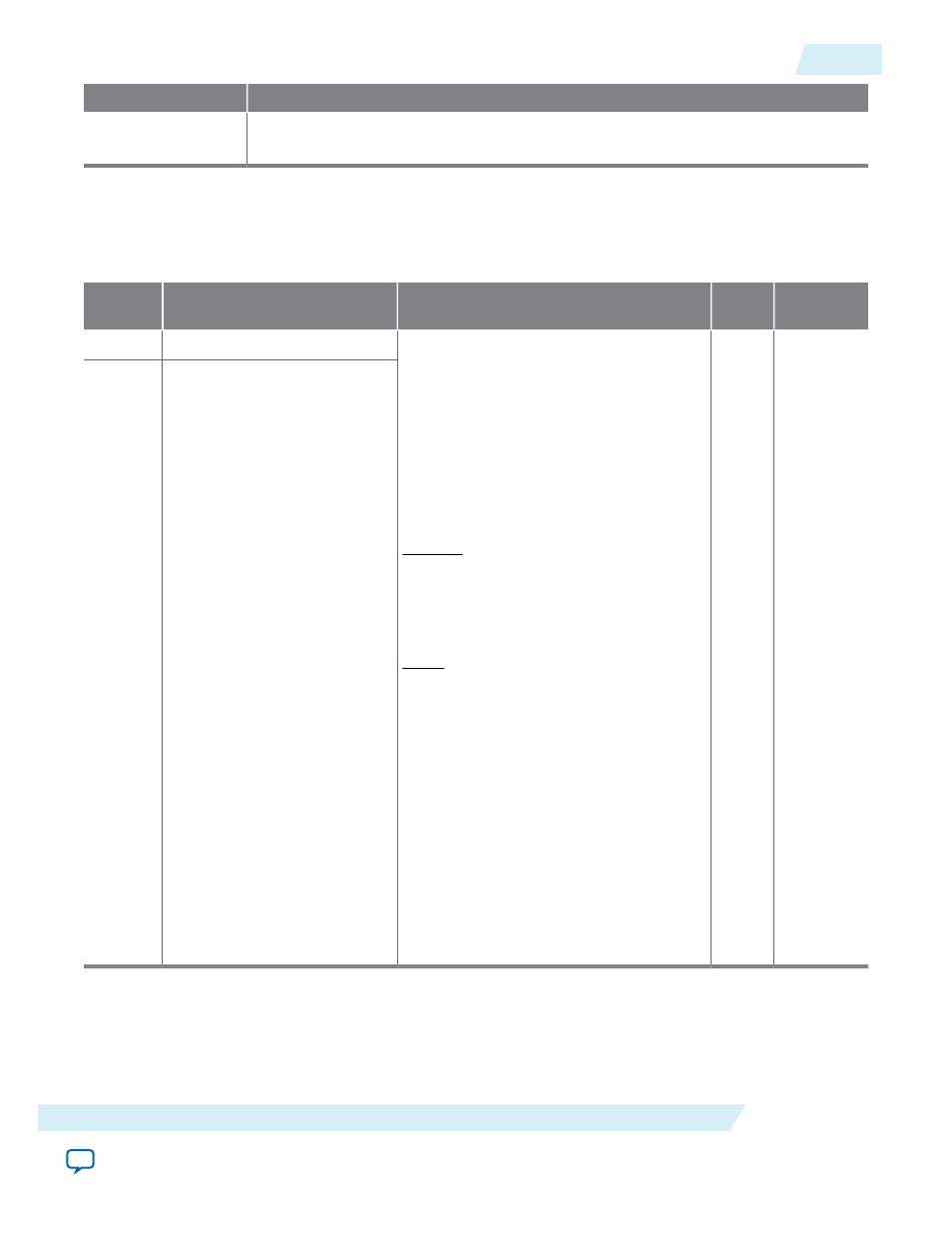

Table 4-4: Primary MAC Address

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x0010

primary_mac_addr0

6-byte primary MAC address. Configure

this register with a non-zero value before

you enable the MAC IP core for operations.

Map the primary MAC address as follows:

•

primary_mac_addr0

: Lower four bytes

of the address.

•

primary_mac_addr1[15:0]

: Upper two

bytes of the address.

•

primary_mac_addr1[31:16]

: Reserved.

Example

If the primary MAC address is 00-1C-23-

17-4A-CB, set

primary_mac_addr0

to

0x23174ACB and

primary_mac_addr1

to

0x0000001C.

Usage

On transmit, the MAC IP core uses this

address to fill the source address field in

control frames. For data frames from the

client, the MAC IP core replaces the source

address field with the primary MAC address

when the

tx_src_addr_override

register

is set to 1.

On receive, the MAC IP core uses this

address to filter unicast frames when the

EN_ALLUCAST

bit of the

rx_frame_control

register is set to 0. The MAC IP core drops

frames whose destination address is

different from the value of the primary

MAC address.

RW

0x0

0x0011

primary_mac_addr1

MAC Reset Control Register

This register is used only in 10G, 1G/10G, and 10M/100M/1G/10G operating modes.

UG-01144

2014.12.15

Primary MAC Address

4-5

Configuration Registers for LL Ethernet 10G MAC

Altera Corporation