Ieee 1588v2 ingress receive signals, Ieee 1588v2 ingress receive signals -23 – Altera Low Latency Ethernet 10G MAC User Manual

Page 105

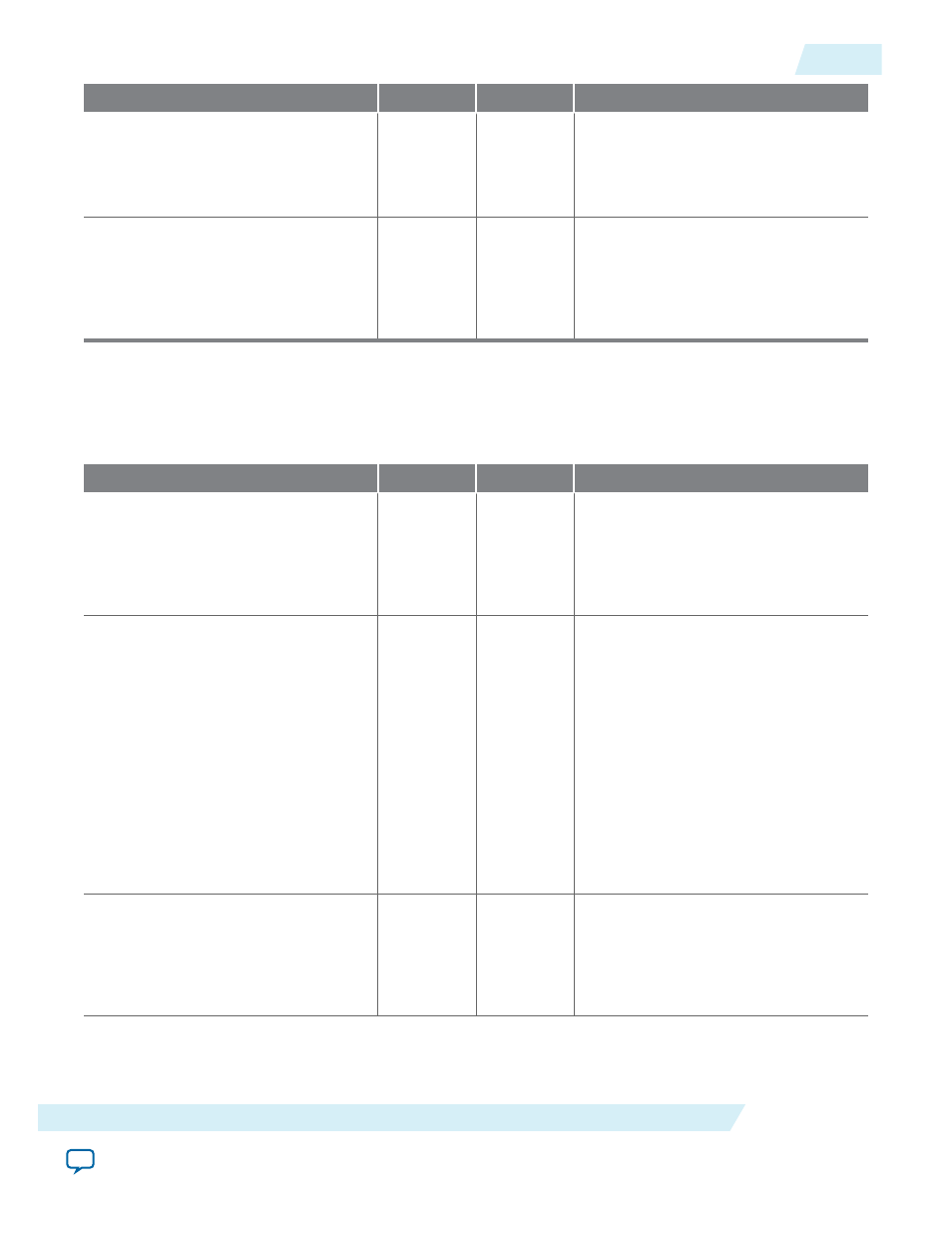

Signal

Direction

Width

Description

tx_etstamp_ins_ctrl_offset_

checksum_field[]

In

16

The location of the checksum field,

relative to the first byte of the packet.

Assert this signal in the same clock

cycle as the start of packet (avalon_

st_tx_startofpacket is asserted).

tx_etstamp_ins_ctrl_offset_

checksum_correction[]

In

16

The location of the checksum

correction field, relative to the first

byte of the packet. Assert this signal

in the same clock cycle as the start of

packet (avalon_st_tx_startofpacket is

asserted).

IEEE 1588v2 Ingress Receive Signals

The signals below are present when you select the Enable time stamping option.

Table 5-19: IEEE 1588v2 Ingress Receive Signals

Signal

Direction

Width

Description

rx_ingress_timestamp_96b_valid

Out

1

When asserted, this signal qualifies

the timestamp on

rx_ingress_

timestamp_96b_data[]

. The MAC

IP core asserts this signal in the same

clock cycle it asserts

avalon_st_rx_

startofpacket

.

rx_ingress_timestamp_96b_data[]

Out

96

Carries the 96-bit ingress timestamp

in the following format:

• Bits 48 to 95: 48-bit seconds field

• Bits 16 to 47: 32-bit nanoseconds

field

• Bits 0 to 15: 16-bit fractional

nanoseconds field

The 96-bit timestamp is usually for

noting the complete ToD and is

useful in ordinary clock and

boundary clock devices. The

transparent clock typically uses 64-bit

timestamp.

rx_ingress_timestamp_64b_valid

Out

1

When asserted, this signal qualifies

the timestamp on

rx_ingress_

timestamp_64b_data[]

. The MAC

IP core asserts this signal in the same

clock cycle it asserts

avalon_st_rx_

startofpacket

.

UG-01144

2014.12.15

IEEE 1588v2 Ingress Receive Signals

5-23

Interface Signals for LL Ethernet 10G MAC

Altera Corporation