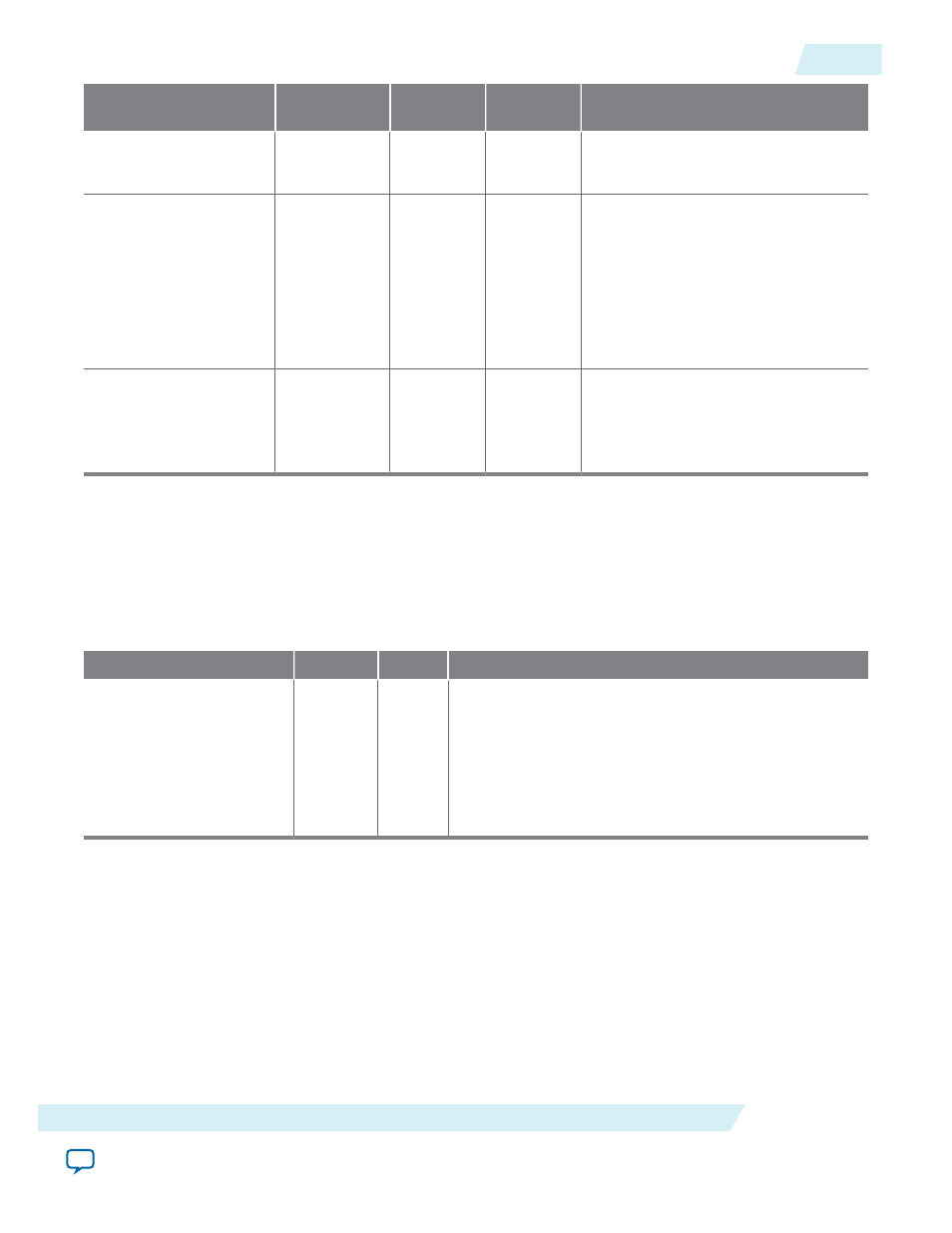

Speed selection signal, Error correction signals, Speed selection signal -3 – Altera Low Latency Ethernet 10G MAC User Manual

Page 85: Error correction signals -3

Signal

Operating

Mode

Direction

Width

Description

rx_rst_n

All

In

1

Active-low reset for the MAC RX

datapath.

csr_clk

10G, 1G/10G,

10M/100M/

1G/10G

In

1

Clock for the Avalon-MM control

and status interface. Altera

recommends that this clock operates

within 125 - 156.25 MHz. A lower

frequency might result in inaccurate

statistics especially when you are

using register-based statistics

counters.

csr_rst_n

All

In

1

Active-low asynchronous reset

signal for the

csr_clk

domain. This

signal acts as a global reset for the

MAC IP core.

Related Information

Speed Selection Signal

Table 5-2: Speed Selection Signal

Signal

Direction

Width

Description

speed_sel

In

2

Connect this signal to the PHY to obtain the PHY's

speed:

• 0x0 = 10 Gbps

• 0x1 = 1 Gbps

• 0x2 = 100 Mbps

• 0x3 = 10 Mbps

Error Correction Signals

The error correction signals are present only when you turn on the ECC option.

UG-01144

2014.12.15

Speed Selection Signal

5-3

Interface Signals for LL Ethernet 10G MAC

Altera Corporation