Altera Low Latency Ethernet 10G MAC User Manual

Page 55

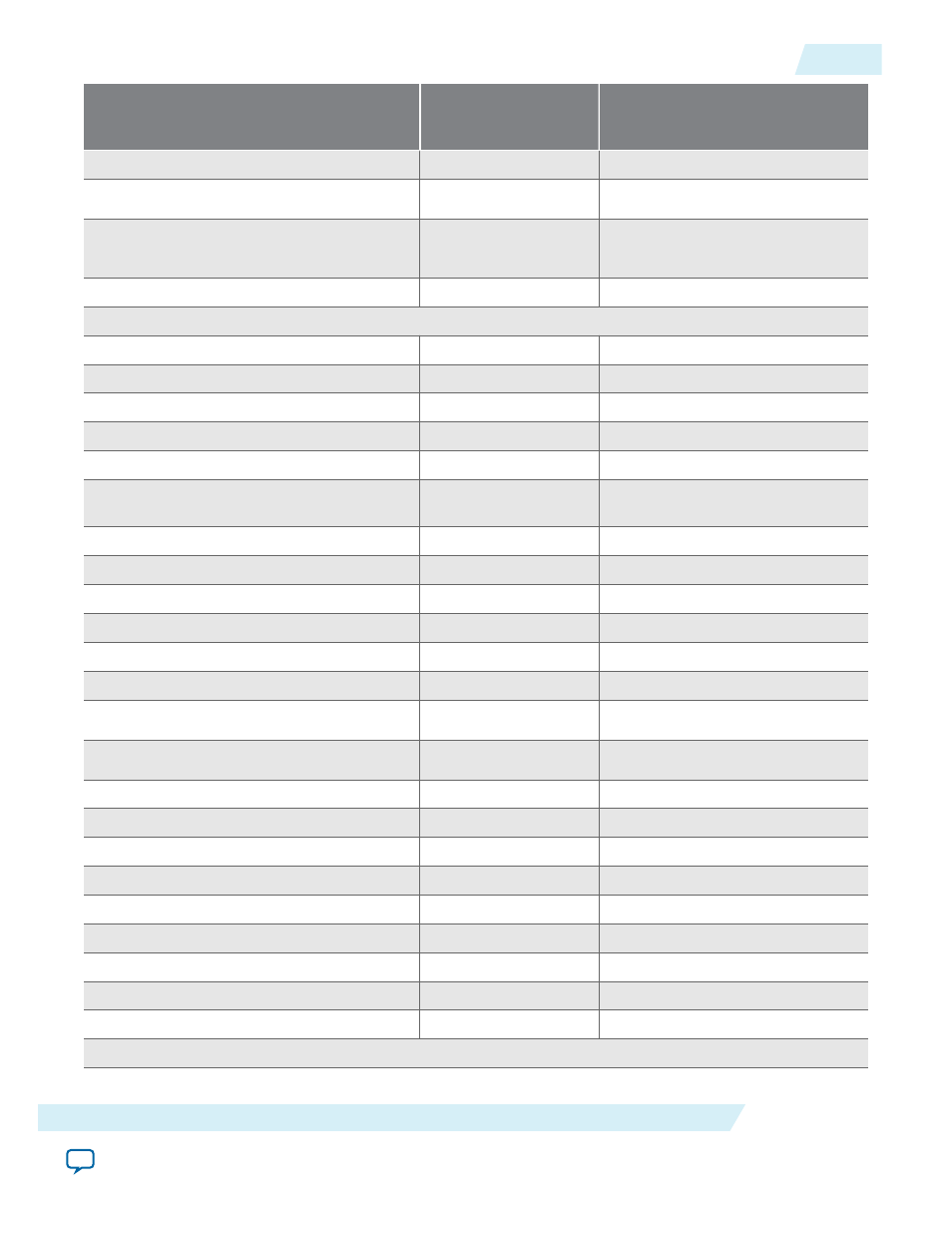

Register Names (10-Gbps Ethernet MAC)

Offset

(10-Gbps Ethernet MAC)

Offset

(LL Ethernet 10G MAC)

TX Address Insertion Control

1200

02A

TX Address Insertion MAC Address[31:0]

1201

010

TX Address Insertion MAC MAC

Address[47:32]

1202

011

TX Maximum Frame Length

1801

02C

MAC RX Configuration Registers

RX Transfer Control

0000

0A0

RX Transfer Status

0001

Not used

RX Pad/CRC Control

0040

0A4

RX CRC Check Control

0080

0A6

RX Overflow Truncated Packet Count[31:0]

00C0

0FC

RX Overflow Truncated Packet

Count[35:32]

00C1

0FD

RX Overflow Dropped Packet Count[31:0]

00C2

0FE

RX Overflow Dropped Packet Count[35:32]

00C3

0FF

RX Preamble Forward Control

0100

0A8

RX Preamble Pass-Through Mode Control

0140

0AA

RX Frame Filtering Control

0800

0AC

RX Maximum Frame Length

0801

0AE

RX Frame MAC Address[31:0]

0802

010

RX Frame MAC Address[47:32]

0803

011

RX Supplementary Address 0[31:0]

0804

0B0

RX Supplementary Address 0[47:32]

0805

0B1

RX Supplementary Address 1[31:0]

0806

0B2

RX Supplementary Address 1[47:32]

0807

0B3

RX Supplementary Address 2[31:0]

0808

0B4

RX Supplementary Address 2[47:32]

0809

0B5

RX Supplementary Address 3[31:0]

080A

0B6

RX Supplementary Address 3[47:32]

080B

0B7

RX PFC Control

0818

0C0

TX Time Stamp Registers

UG-01144

2014.12.15

Mapping 10-Gbps Ethernet MAC Registers to LL Ethernet 10G MAC Registers

4-3

Configuration Registers for LL Ethernet 10G MAC

Altera Corporation