Register access, Register access -4 – Altera Low Latency Ethernet 10G MAC User Manual

Page 56

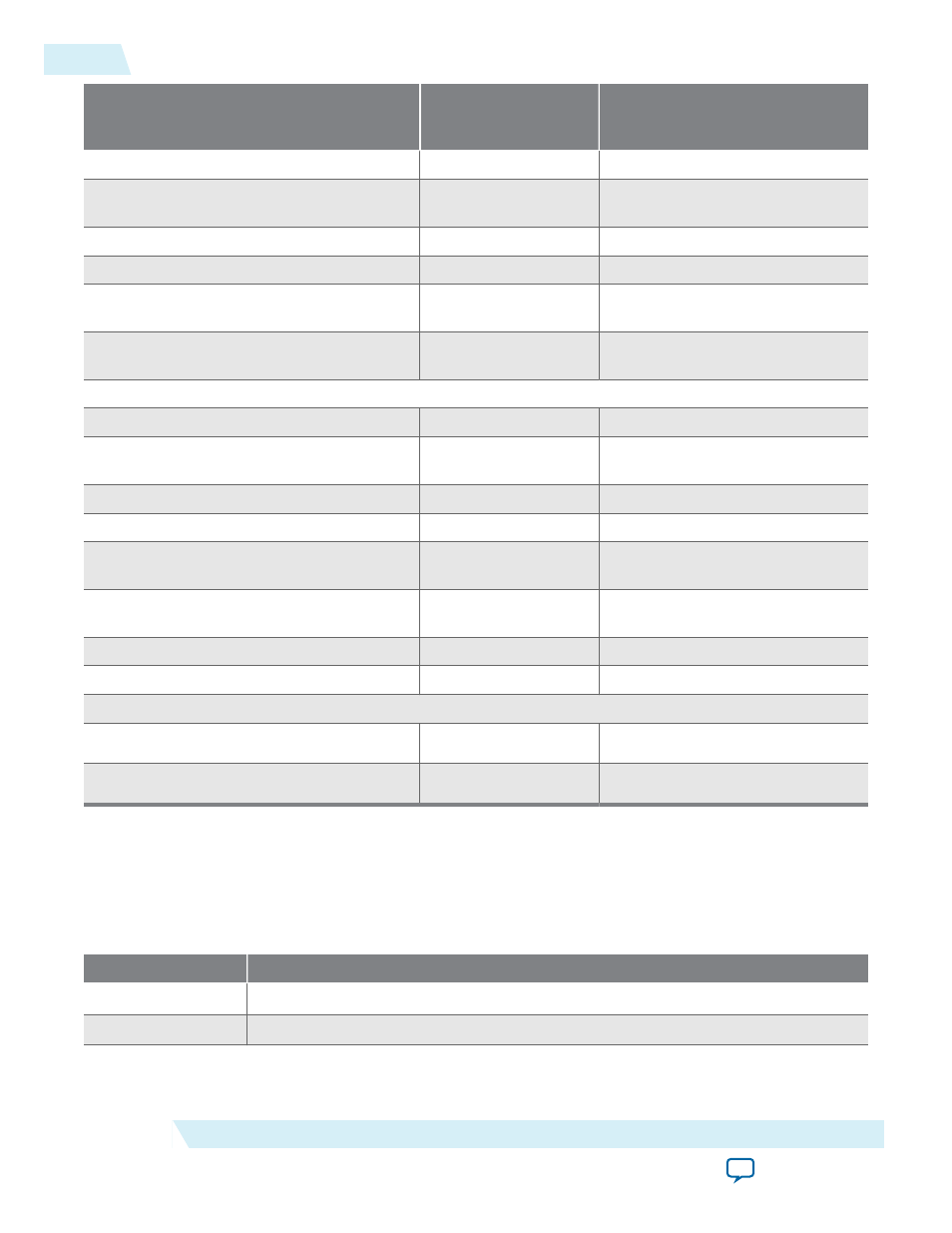

Register Names (10-Gbps Ethernet MAC)

Offset

(10-Gbps Ethernet MAC)

Offset

(LL Ethernet 10G MAC)

TX Period for 10G

1110

100

TX Fractional Nano-second Adjustment for

10G

1112

102

TX Nano-second Adjustment for 10G

1113

104

TX Period for 10M/100M/1G

1118

108

TX Fractional Nano-second Adjustment for

10M/100M/1G

111A

10A

TX Nano-second Adjustment for 10M/

100M/1G

111B

10C

RX Time Stamp Registers

RX Period for 10G

0110

120

RX Fractional Nano-second Adjustment for

10G

0112

122

RX Nano-second Adjustment for 10G

0113

124

RX Period for 10M/100M/1G

0118

128

RX Fractional Nano-second Adjustment for

10M/100M/1G

011A

12A

RX Nano-second Adjustment for 10M/

100M/1G

011B

12C

All TX Statistics Registers

1Cxx

14x

All RX Statistics Registers

0Cxx

1Cx

Status Registers

ECC Error Status

Not applicable

240

ECC Error Enable

Not applicable

241

Register Access

The following table defines the register access.

Table 4-3: Register Access

Access

Definition

RO

Read only. The value of the register may vary.

RW

Read and write.

4-4

Register Access

UG-01144

2014.12.15

Altera Corporation

Configuration Registers for LL Ethernet 10G MAC