Altera Low Latency Ethernet 10G MAC User Manual

Page 32

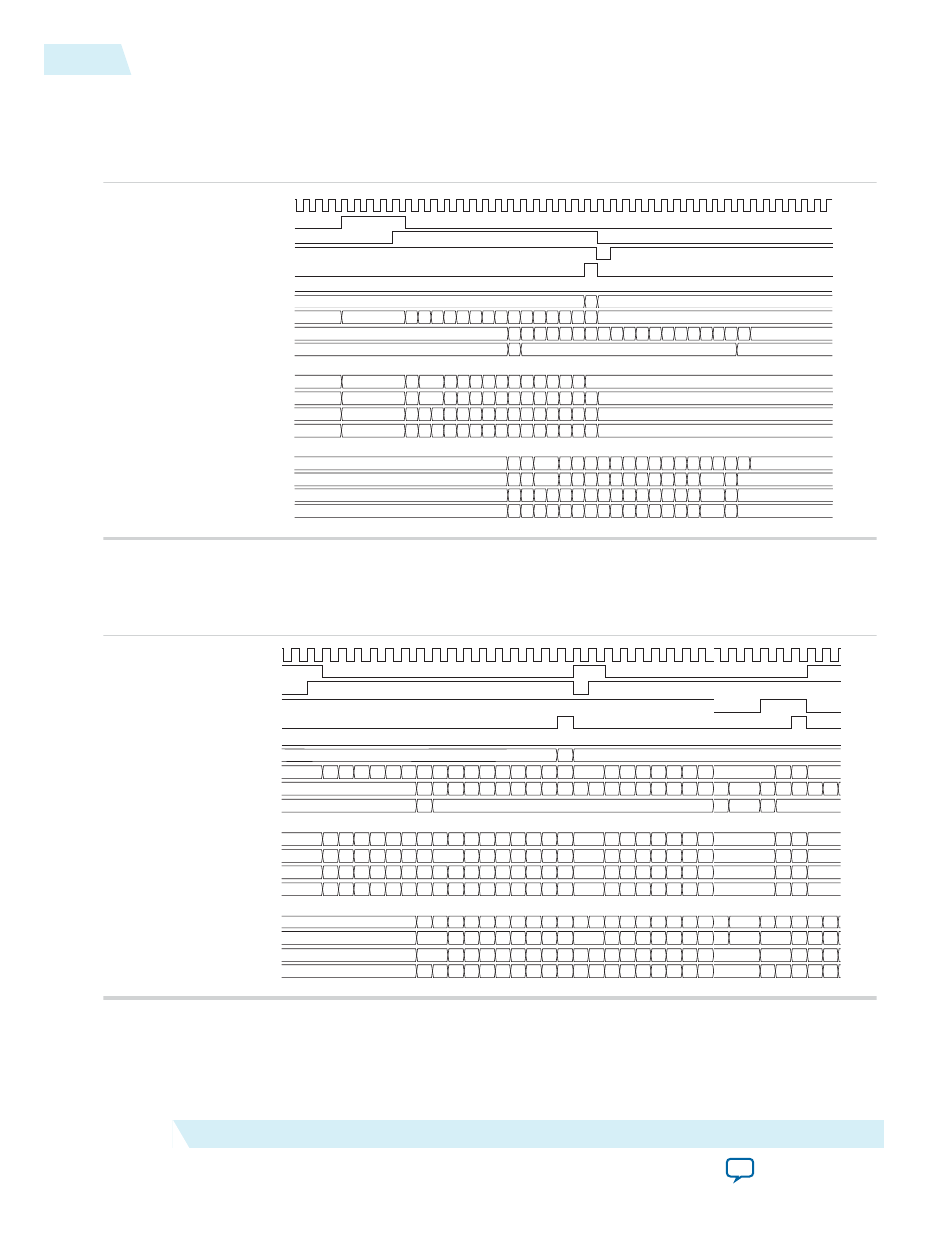

Figure 3-8: Normal Frame with Preamble Passthrough Mode, Padding Bytes Insertion, and Source

Address Insertion Enabled

The following diagram shows the transmission of good frames with preamble passthrough mode, padding

bytes insertion, and source address insertion enabled.

0

3

7c91_5b8d

*5

*_fff *fb

*4 *5 *3 *f *0 *9 *a *1 *3 *0 *3 *0

0707_0707

*b *1

*_fff

*ff *2 *0 *b *0 *e *5 *5 *6 *3 *0 *4 *c *0 *8 *d

f

1

7c

d1 ff 2b 00 5b 60 8e 65 25 36 13 10 04

81

bf ff

00

98 2f 5d de 4b 4e 54 53 13 60 a1

83

00

1d 45 e3 5b 09 bb db 10 e8 86 a9

d5

00

24 f5 f3 2f 20 69 ba 21 53 f0 83

ff 44

ff fb

5b

8d

fb

04

22 00 5b 60 8e 65 25 36 13 10

d1 ff

07

fd

7c 00 38

*5

a1

33 2f 5d de 4b 4e 54 53 13 60

*5 ff

07

00 7a

*5

a9

44 45 e3 5b 09 bb db 10 e8 86

*5

07

00 9c

ff 00

*5

83

55 f5 f3 2f 20 69 ba 21 53 f0

*5

07

00 ee

ff 00

tx_312_5_clk

avalon_st_tx_startofpacket

avalon_st_tx_valid

avalon_st_tx_ready

avalon_st_tx_endofpacket

avalon_st_tx_error

avalon_st_tx_empty[1:0]

avalon_st_tx_data[31:0]

xgmii_tx_data[31:0]

xgmii_tx_control[3:0]

avalon_st_tx_data[31:24]

avalon_st_tx_data[23:16]

avalon_st_tx_data[15:8]

avalon_st_tx_data[7:0]

xgmii_tx_data[7:0]

xgmii_tx_data[15:8]

xgmii_tx_data[23:16]

xgmii_tx_data[31:24]

0

92e6_9b29

0faa_4s5e

92

0f

e6

aa

9b

4a

29

5e

0707_0707

f

0

07

07

07

07

Figure 3-9: Back-to-back Transmission of Normal Frames with Source Address Insertion Enabled.

The following diagram shows back-to-back transmission of normal frames with source address insertion

enabled. The MAC primary address registers are set to 0x000022334455.

0

3

0

8190_a0b0 *a7 *8d *ed *05 *56 *f0 *d6 *44 *95 *f4 *38 *03 *31 *0b *7a *00 *0_a0b0 *d2 *96 *01 *5c *43 *cb *e3

b4c1_cafd

*f0 *4c 0023_456

0707_0707

*fb *55 *81 *c0 *22 *3d *f5 *08 *d6 *7e *51 *37 *1a *95 *a2 *9f *96 *b9 *e3 *be *7_0707 *fb *55 *81 *c0 *22

f

1

0

e

f

1

0

81

c0 15 3d f5 08 d6 7e 51 37 1a 95 a2 31 96 b9 e3

81

c0 d6 88 00 7b 31 0e

b4

49 25

00

90

d0 83 61 1c 75 e3 f4

7b

99 cd bc 83 85 5a 00

90

d0 07 08 0a 40 9f 76

c1

04 8b

23

a0

e7 35 1b 2f ff 5a b1 fc 06 b2 a8 ca 54 0d 4f 00

a0

cd 39 00 1d 05 11 57

ca

e1 27

45

b0

a7 8d ed 05 56 f0 d6 44 95 f4 38 ca 31 0b 7a 00

b0

d2 96 01 5c 43 cb e3

fd

f0 4c

67

07

fb 55 81 c0 22 3d f5 08 d6 7e 51 37 1a 95 a2 9f 96 b9 e3 be

07

fb 55 81 c0 22

07

55

90 d0 33 61 1c 75 e3 f4

7b

99 cd bc 83 85 5a c7 fd

07

55

90 d0 33

07

55

a0 00 44 1b 2f ff 5a b1 fc 06 b2 a8 ca 54 0d 4f 53

07

55

a0 00 44

07

55 d5 b0 00 55 ed 05 56 f0 d6 44 95 f4 38 03 31 0b 7a 88

07

55 d5 b0 00 55

tx_312_5_clk

avalon_st_tx_startofpacket

avalon_st_tx_valid

avalon_st_tx_ready

avalon_st_tx_endofpacket

avalon_st_tx_error

avalon_st_tx_empty[1:0]

avalon_st_tx_data[31:0]

xgmii_tx_data[31:0]

xgmii_tx_control[3:0]

avalon_st_tx_data[31:24]

avalon_st_tx_data[23:16]

avalon_st_tx_data[15:8]

avalon_st_tx_data[7:0]

xgmii_tx_data[7:0]

xgmii_tx_data[15:8]

xgmii_tx_data[23:16]

xgmii_tx_data[31:24]

3-10

TX Timing Diagrams

UG-01144

2014.12.15

Altera Corporation

Functional Description of LL Ethernet 10G MAC