Altera LVDS SERDES Transmitter / Receiver User Manual

Page 20

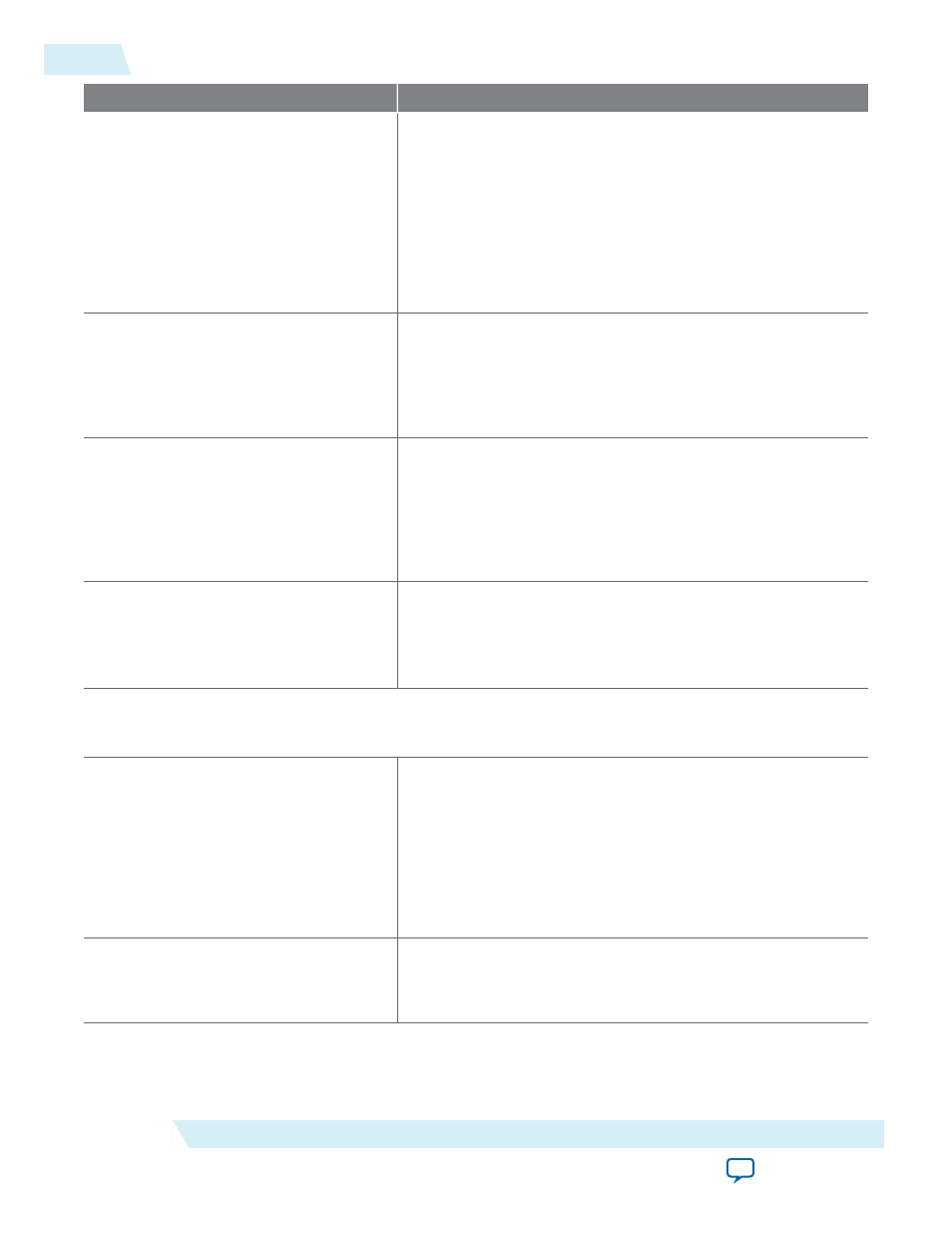

Option

Description

Use source-synchronous mode of the

PLL

Turn on this option to ensure that the IP core instance makes

the required phase adjustment to guarantee a consistent

relationship between the clock and the data, at the capture

register and at the pin.

Always turn on this option, unless you have performed all of

the necessary phase adjustments manually. Altera recommends

that you turn on this option when you use non-dedicated

SERDES schemes. This option is only available when you

implement the SERDES in LEs.

Align clock to center of data window at

capture point

Turn on this option to add a phase shift of 90° to the clock,

which center-aligns the clock in the data.

This option is only available for Arria GX, Cyclone II, Stratix II

GX, Stratix II, and HardCopy II devices when you implement

the SERDES in logic cells.

Enable self-reset on lost lock in the PLL Turn on this option to reset the PLL automatically when the

PLL loses lock.

This option is only available for Arria II GX, Arria II GZ,

HardCopy III, HardCopy IV, Stratix III, Stratix IV, Cyclone III

and Cyclone IV devices when you implement the SERDES in

logic cells.

Enable FIFO for DPA channels

The phase-compensation FIFO buffer synchronizes parallel

data to the global clock domain of the core.

This option is only available in Stratix GX devices when you

turn on the DPA mode.

DPA Settings 1 (page 5)

The options on this page are available when you turn on the DPA mode.

Use 'rx_divfwdclk' output port and

bypass the DPA FIFO

Turn on this option to divide the DPA clock by the deserializa‐

tion factor and then forward the DPA clock to the core. The

DPA clock drives the bit-slip and alignment circuitry,

bypassing the FIFO.

Turn on this option for soft-CDR mode. This option is

available in Arria II GX, Arria II GZ, Arria V, Arria V GZ,

HardCopy III, HardCopy IV, Stratix III, Stratix IV, and Stratix

V devices only.

What is the simulated recovered clock

phase drift?

Models a phase drift in the recovered clock. Clock phase drift is

expressed as the equivalent number of full clock cycles of drift

for every parts per million (PPM) clock cycles. The value for

this option can be positive, negative or zero.

20

ALTLVDS_RX Parameter Settings

UG-MF9504

2014.12.15

Altera Corporation

LVDS SERDES Transmitter/Receiver IP Cores User Guide