Document revision history – Altera LVDS SERDES Transmitter / Receiver User Manual

Page 67

Generating ALTLVDS IP Core Using Clear Box Generator

Apart from the IP core parameter editor, you can also use the clear box generator, a command-line

executable, to configure parameters that are in the ALTLVDS_TX and ALTLVDS_RX parameter editors.

The clear box generator creates or modifies custom IP core variations that you can instantiate in a design

file. The clear box generator generates IP core variation file in Verilog HDL or VHDL format.

1. Create a text file (.txt) that contains your clear box ports and parameter settings in your working

directory.

2. Open the command prompt and change the current directory to your working directory by typing:

cd

c:\altera\11.0\quartus\work\

The clear box executable file name is clearbox.exe.

3. To view the available ports and parameters for this IP core, type one of the following commands:

clearbox altlvds_tx -h

or

clearbox altlvds_rx -h

.

4. To generate the ALTLVDS_TX and ALTLVDS_RX IP cores variation file based on the ports and

parameter settings in the text file, type one of the following commands:

clearbox altlvds_tx

-f *.txt

or

clearbox altlvds_rx -f *.txt

.

For example,

clearbox altlvds_tx -f sample_param_test.txt

5. After the clear box generator generates the IP core variation files, instantiate the IP core module in a

HDL file or a block diagram file in the Quartus II software.

6. To view the estimated hardware resources that the ALTLVDS_TX and ALTLVDS_RX IP cores use,

type one of the following commands:

clearbox altlvds_tx -f

sample_param_test.txt -resc_count

or

clearbox altlvds_rx -f

sample_param_test.txt -resc_count

.

This command does not generate a HDL file.

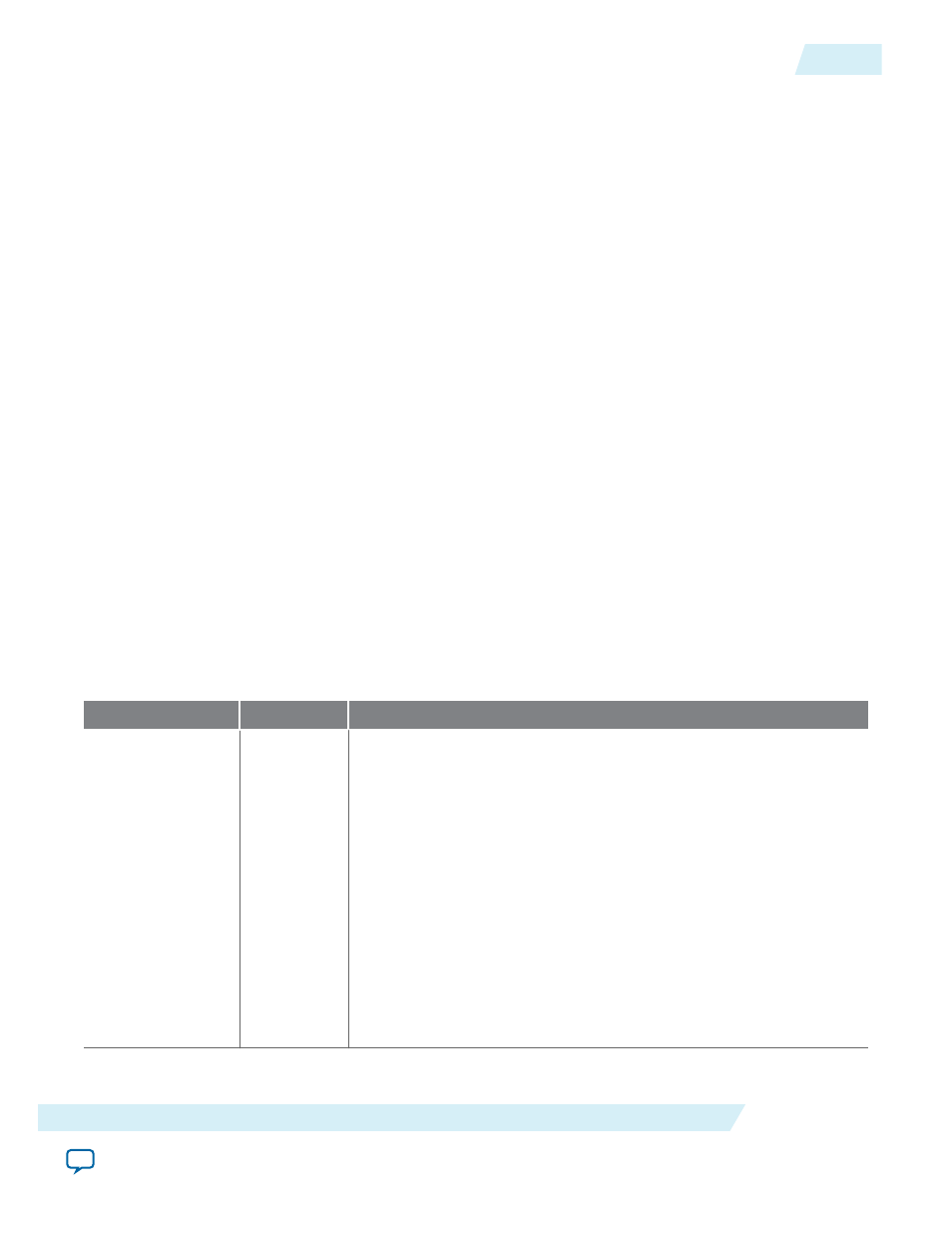

Document Revision History

Date

Version

Changes

December 2014

2014.12.15 • Added footnotes to clarify the availability of DPA and soft-CDR

modes in Stratix series.

• Removed Cyclone series from the list of series with soft-CDR

support.

• Added guidelines about the time required for tx_outclock to

stabilize if you turn on the Implement Deserializer circuitry in

logic cells option.

• Updated the statement that refers to selecting "Left/Right PLL" to

set up PLL in LVDS mode to clarify that the option is required only

for Arria II devices.

• Updated information about the PLL IP core to clarify that for

Stratix IV, Arria II, and Cyclone IV devices, the PLL IP core is

ALTPLL IP, and for Stratix V, Arria V, and Cyclone V devices, the

PLL IP core is Altera PLL.

UG-MF9504

2014.12.15

Generating ALTLVDS IP Core Using Clear Box Generator

67

LVDS SERDES Transmitter/Receiver IP Cores User Guide

Altera Corporation