Installing and licensing ip cores – Altera LVDS SERDES Transmitter / Receiver User Manual

Page 3

For the Stratix series, the side I/O banks contain dedicated SERDES circuitry, which includes the PLLs,

serial shift registers, and parallel registers. The transmit and receive functions use varying numbers of LEs

depending on the number of channels, serialization, and deserialization factors. For best performance,

manually place these LEs in columns as close as possible to the SERDES circuitry and LVDS pins. By

default, the Quartus II software places these LEs automatically during placement and routing.

Note: When dedicated SERDES is implemented in LVDS transmitter, the SERDES is directly connected

to the LVDS transmitter; therefore, the output of the transmitter cannot be assigned to single-

ended I/O standards.

Note: The Quartus II software reports the number of LEs used per ALTLVDS block in the Fitter

Resource Utilization by Entity section in the Resource section of the Compilation Report.

The Cyclone series uses DDIO registers as part of the SERDES interface. Because data is clocked on both

the rising edge and falling edge, the clock frequency must be half the data rate; therefore, the PLL runs at

half the frequency of the data rate. The core clock frequency for the transmitter is data rate divided by

serialization factor (J). For the odd serialization factors, depending on the output clock-divide factor (B)

and device family, an optional core clock frequency of data rate divided by two times the serialization

factor (J) is also available.

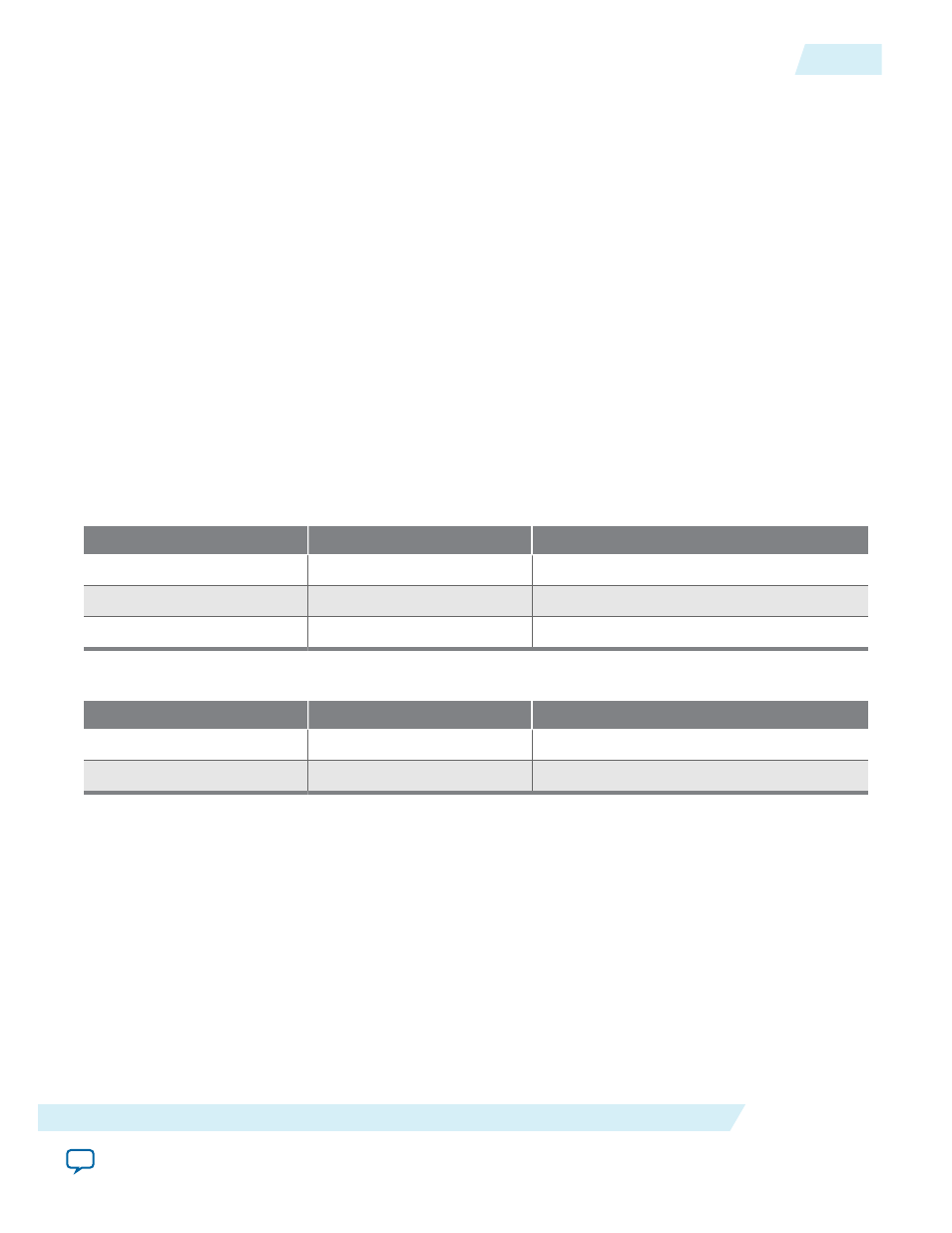

Use the following tables to determine the clock and data rate relationships.

Table 2: Cyclone Series ALTLVDS Transmitter Clock Relationships

Clock Type

J = Even

J = Odd

Fast Clock

Data Rate / 2

Data Rate / 2

Slow Clock (outclock)

Data Rate / 2 * B

Data Rate / 2 * B

Core Clock

Data Rate / J

Data Rate / J

Table 3: Cyclone Series ALTLVDS Receiver Clock Relationships

Clock Type

J = Even

J = Odd

Fast Clock

Data Rate / 2

Data Rate / 2

Slow Clock (outclock)

Data Rate / J

Data Rate / J

Related Information

Installing and Licensing IP Cores

The Altera IP Library provides many useful IP core functions for production use without purchasing an

additional license. You can evaluate any Altera

®

IP core in simulation and compilation in the Quartus

®

II

software using the OpenCore

®

evaluation feature. Some Altera IP cores, such as MegaCore

®

functions,

require that you purchase a separate license for production use. You can use the OpenCore Plus feature to

evaluate IP that requires purchase of an additional license until you are satisfied with the functionality and

UG-MF9504

2014.12.15

Installing and Licensing IP Cores

3

LVDS SERDES Transmitter/Receiver IP Cores User Guide

Altera Corporation