Altera LVDS SERDES Transmitter / Receiver User Manual

Page 50

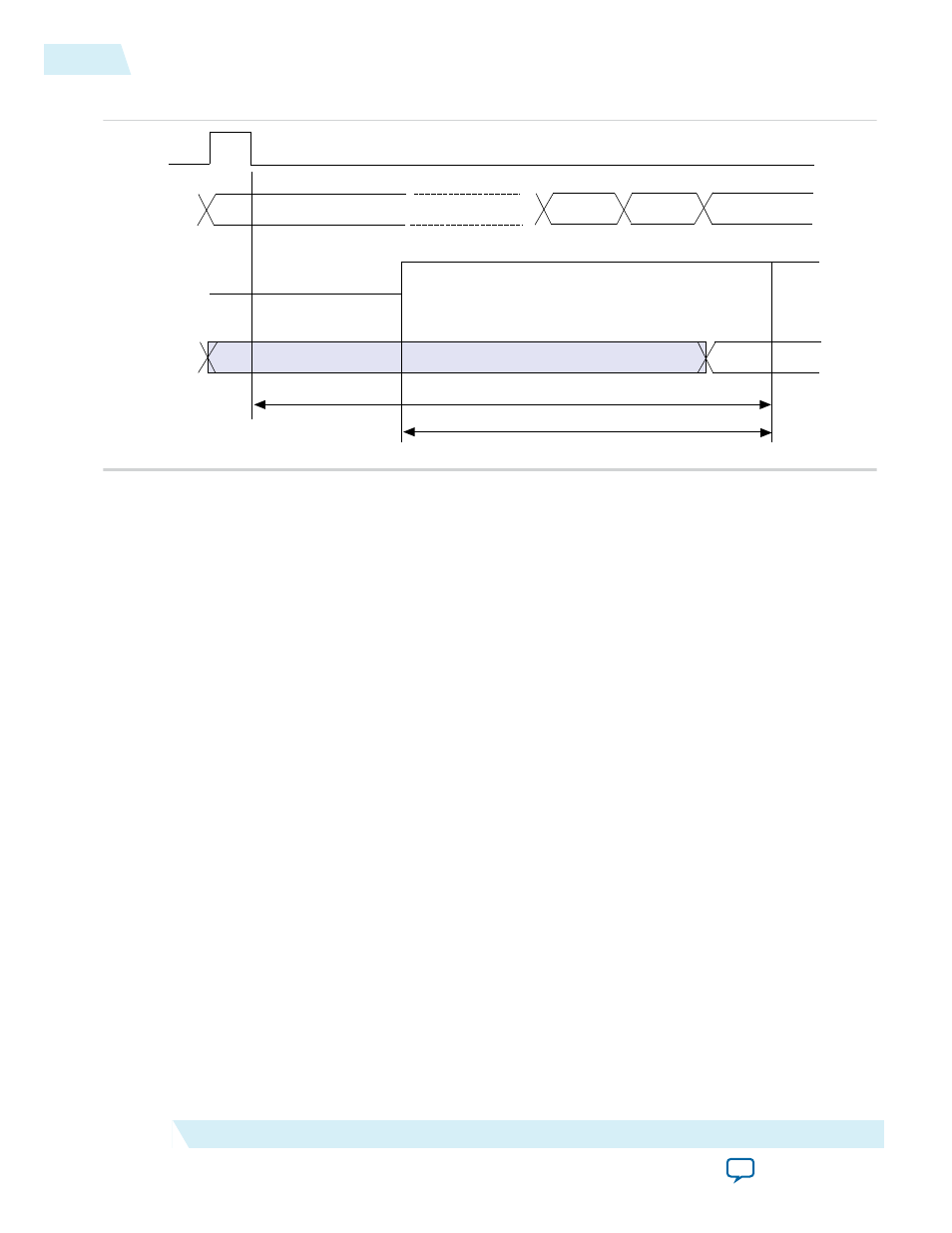

Figure 9: DPA Misalignment Issue

DPA takes much longer time than anticipated to lock

to the optimum phase of 3

Invalid Data *

0

1

2

3

rx_reset

Valid Data

rx_dpa_locked asserts before DPA has locked to its optimum phase

DPA

Phase

rx_dpa_locked

In the Quartus II software versions 9.0 and later, the DPA PLL calibration feature is added to the

ALTLVDS_RX IP core to overcome the DPA misalignment issue found in Stratix IV ES devices; the

Stratix IV production devices are not affected. The DPA PLL calibration feature is available when the

LVDS receiver is configured in DPA or soft-CDR mode. DPA PLL calibration phase-shifts the PLL

outputs to induce progress in the PLL’s phase-detect up and down counter and to facilitate a new phase

selection.

The following events occur during the DPA PLL calibration process:

1. The ALTLVDS_RX IP core counts 256 data transitions; the PLL calibrates the phase forward by two

clocks.

2. The ALTLVDS_RX IP core counts 256 transitions; the PLL calibrates the phase backward by two

clocks so that the PLL timing returns to normal.

3. The ALTLVDS_RX IP core counts 256 data transitions, and then asserts the

rx_dpa_locked

signal.

Note: For more information about DPA lock time specification, refer to the Device Data Sheet chapter in

the respective device handbook.

Related Information

DPA PLL Calibration in Arria II and Stratix IV Devices and Later

Starting with the Arria II device and the production versions of Stratix IV devices, DPA PLL calibration is

implemented for each receiver channel independently using delay elements in the LVDS receiver path.

Anytime the

rx_reset

port is deasserted for a receiver channel, the DPA circuitry is reset, and the calibra‐

tion and locking process begins. The DPA circuitry in an LVDS receiver can reset at any time without

impacting other LVDS receivers sharing the same PLL.

50

DPA PLL Calibration in Arria II and Stratix IV Devices and Later

UG-MF9504

2014.12.15

Altera Corporation

LVDS SERDES Transmitter/Receiver IP Cores User Guide