Altera LVDS SERDES Transmitter / Receiver User Manual

Page 27

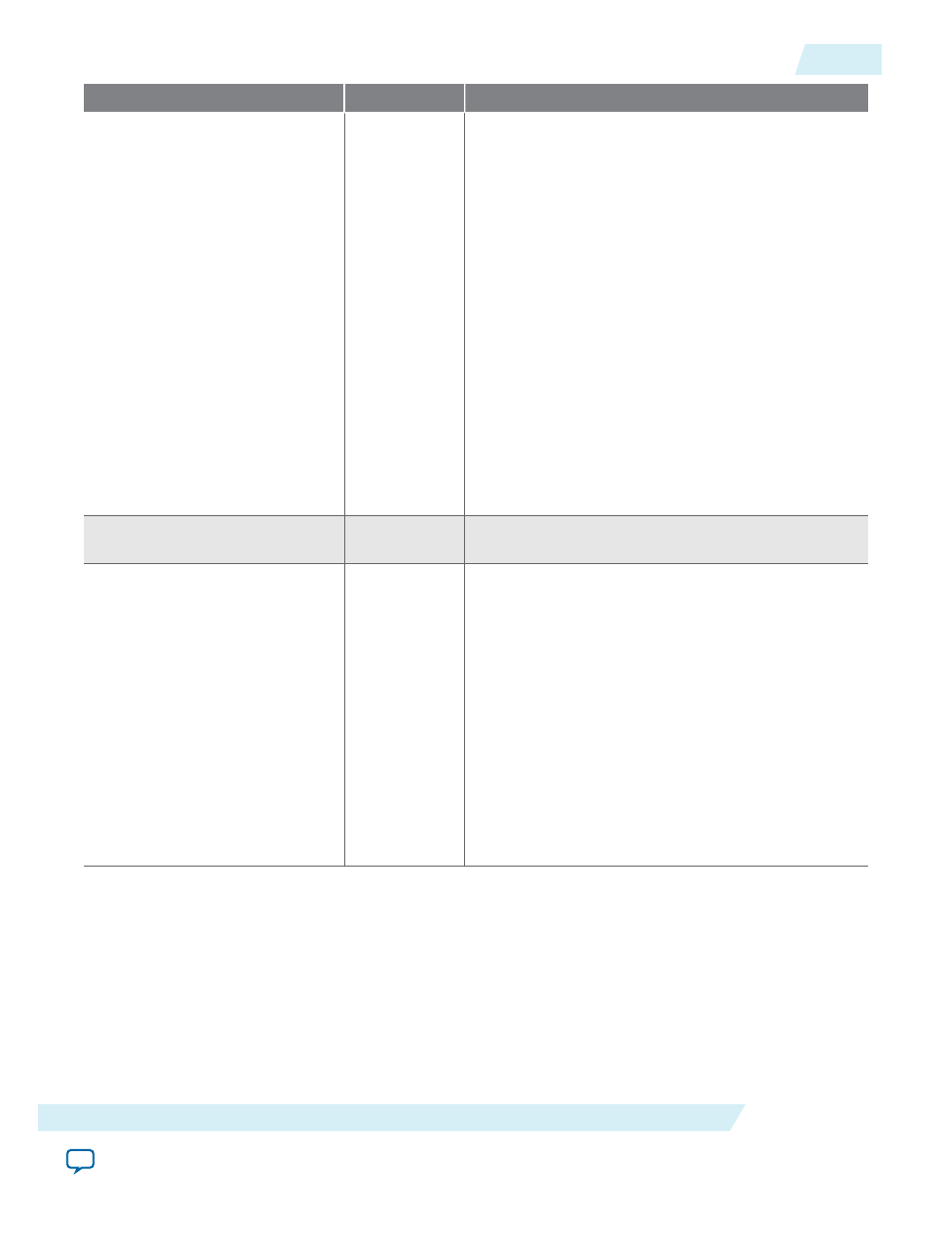

Parameter

Type

Description

deserialization_factor

Integer

Specifies the number of bits per channel.

The following is the device support and its values

with normal mode:

• Arria II GX, Arria II GZ, Arria V, Arria V GZ:

1

to

10

• Arria GX:

1

,

2

,

4

, to

10

• Cyclone, Cyclone II, Cyclone III, Cyclone IV,

Cyclone V:

1

,

2

,

4

, to

10

• HardCopy II, HardCopy III, and HardCopy IV:

1

,

2

,

4

, to

10

• Stratix and Stratix GX:

1

,

2

,

4

,

7

,

8

, to

10

• Stratix II and Stratix II GX:

1

,

2

,

4

, to

10

• Stratix III, Stratix IV, and Stratix V:

1

to

10

Arria GX, Arria II GX, Arria II GZ, HardCopy II,

HardCopy III, HardCopy IV, Stratix, Stratix GX,

Stratix II, Stratix II GX, Stratix III, and Stratix IV

devices have the values of

1

,

2

,

4

, to

10

with SERDES

using logic cells.

enable_clk_latency

String

Specifies whether the PLLs use clock latency. The

values are

ON

and

OFF

.

implement_in_les

String

Specifies whether to implement SERDES circuitry in

logic cells, which allows the circuitry to behave

similarly to Stratix LVDS circuitry. You must use the

implement_in_les

parameter for SERDES functions

that require data rates that are lower than the

dedicated circuitry. The values are

ON

and

OFF

. For

Cyclone, Cyclone II, Cyclone III, and Cyclone IV

devices, the value is always

ON

.

Available for all devices except the MAX series.

The ALTLVDS_TX IP core starts its operation at the

first rising edge of the fast clock, after the PLL has

locked. This is intended for slow speeds and the bit

alignment might be different from a dedicated

SERDES implementation.

UG-MF9504

2014.12.15

Command Line Interface Parameters

27

LVDS SERDES Transmitter/Receiver IP Cores User Guide

Altera Corporation