Altera LVDS SERDES Transmitter / Receiver User Manual

Page 44

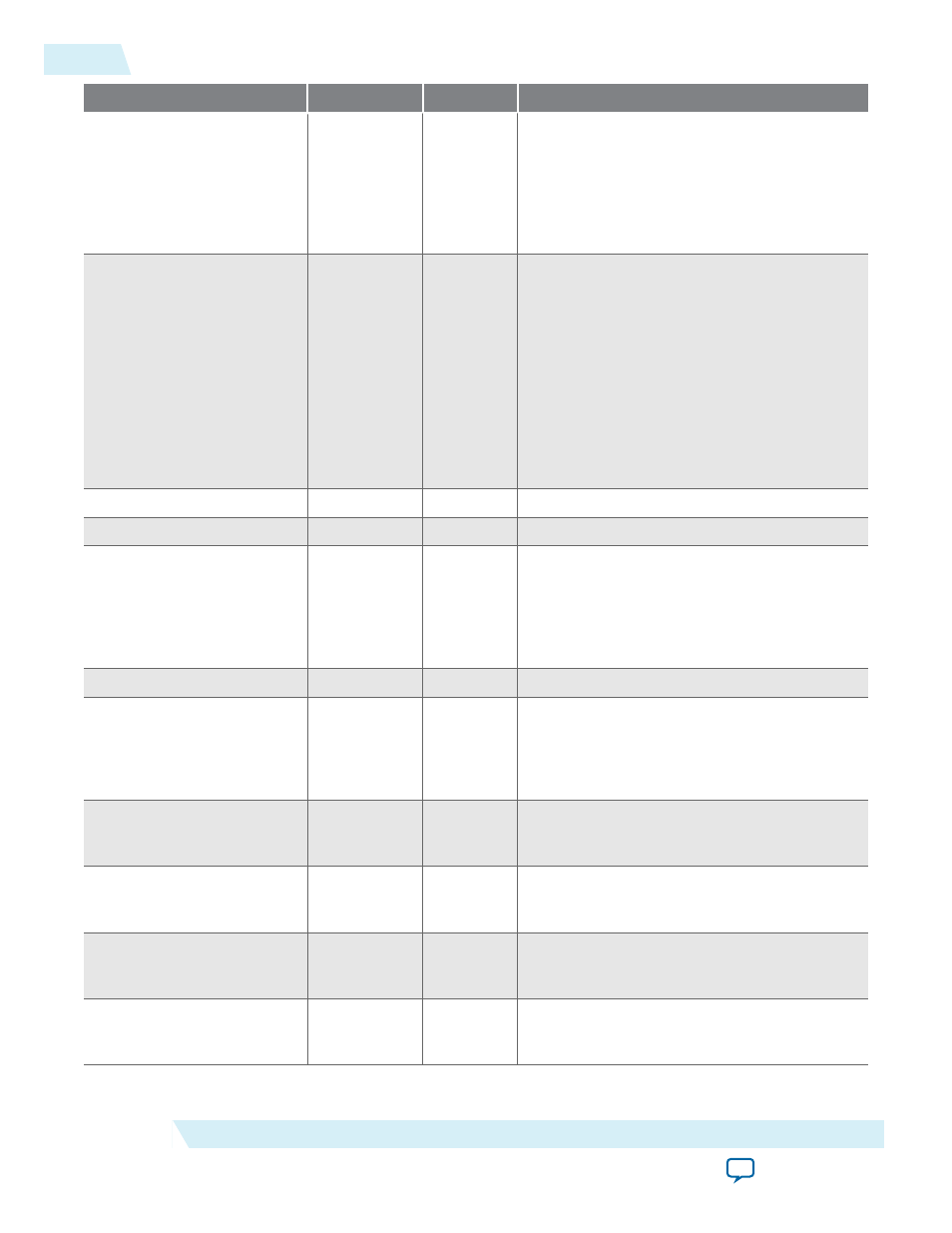

Port Name

Direction

Width (Bit)

Description

rx_in[]

Input

n

LVDS serial data input port of n channels

wide.

rx_in[(n-1)..0]

is deserialized and

driven on

rx_out[(J * n)-1 ..0]

where J is

the deserialization factor and n is the number

of channels.

rx_in[0]

drives data to

rx_

out[(J-1)..0]

.

rx_in[1]

drives data to the

next J number of bits on

rx_out

.

rx_inclock

Input

1

LVDS reference input clock. The parameter

editor automatically selects the appropriate

PLL multiplication factor based on the data

rate and reference clock frequency selection.

When using Stratix II devices in external PLL

mode, connect the

rx_inclock

port to the

sclkout0

or

sclkout1

port. When using

Cyclone and Cyclone II devices in external

PLL mode, connect the

rx_inclock

port to

other clocks. Refer to the respective device

handbook for supported input clock

frequency ranges.

rx_pll_enable

Input

1

Enables control for the LVDS PLL.

rx_readclock

Input

1

Clock input port for reading operation.

rx_reset

Input

n

Asynchronous reset to the DPA circuitry and

FIFO. The minimum pulse width require‐

ment for this reset is one parallel clock cycle.

This signal resets DPA and FIFO blocks. You

can connect this port if the

enable_dpa_mode

parameter is turned on.

rx_syncclock

Input

1

Slow clock input port.

dpa_pll_cal_busy

Output

1

Busy signal that is asserted high when PLL

calibration occurs. PLL clock signals are phase

adjusted for two fast clock cycles ahead.

Available only when DPA mode with PLL

calibration is enabled.

pll_phasecounterselect

Output

1

Specifies the PLL counter select. Available

only when DPA mode with PLL calibration is

enabled.

pll_phasestep

Output

1

Specifies dynamic phase shifting. Available

only when DPA mode with PLL calibration is

enabled.

pll_phaseupdown

Output

1

Specifies dynamic phase adjustment.

Available only when DPA mode with PLL

calibration is enabled.

pll_scanclk

Output

1

Clock signal for the serial scan chain.

Available only when DPA mode with PLL

calibration is enabled.

44

ALTLVDS_RX Ports

UG-MF9504

2014.12.15

Altera Corporation

LVDS SERDES Transmitter/Receiver IP Cores User Guide