Altera LVDS SERDES Transmitter / Receiver User Manual

Page 23

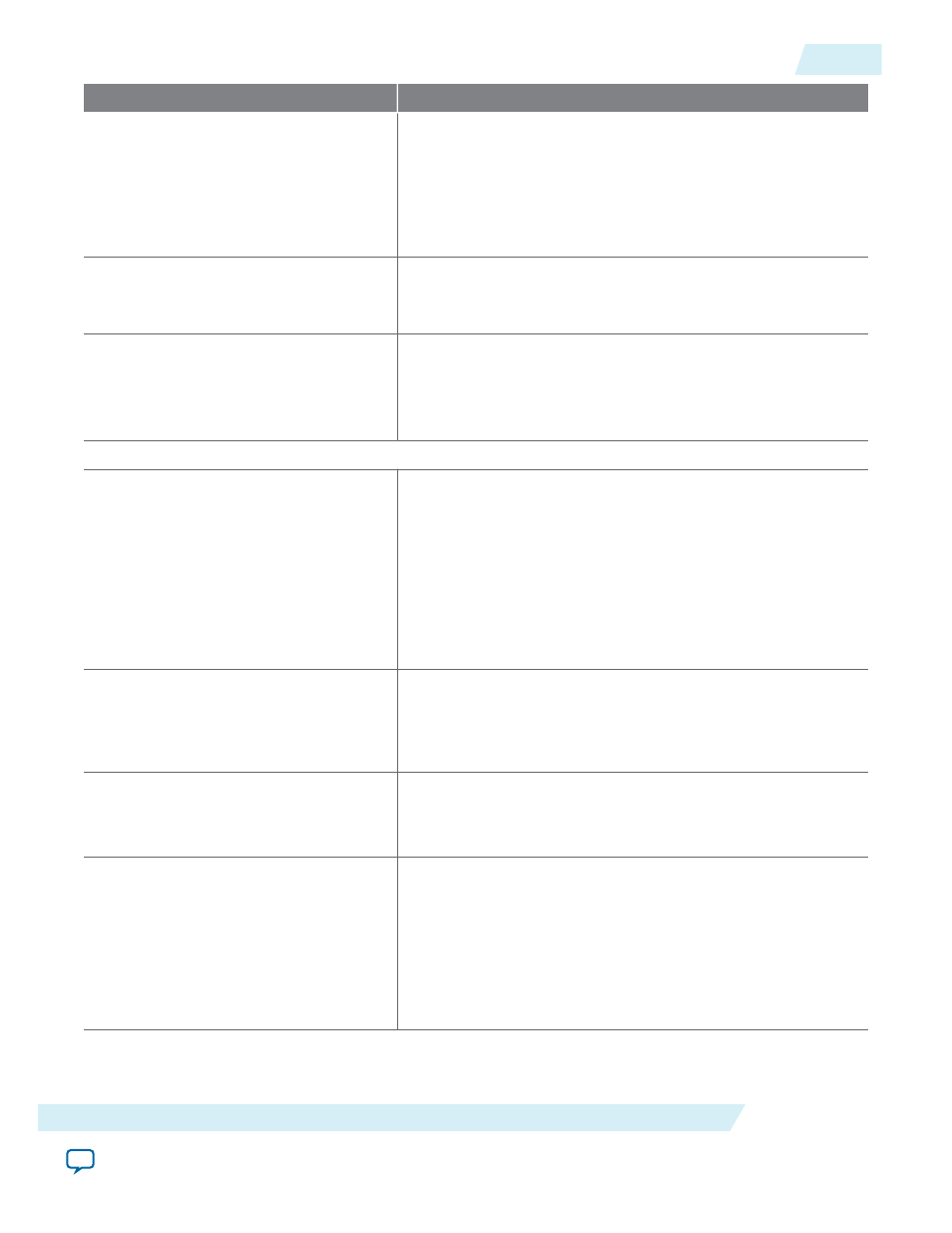

Option

Description

Enable PLL Calibration

Turn on this option to phase-shift the PLL outputs when the

dpa_pll_cal_busy

signal is high. The default setting is OFF.

This option is available for Arria II GZ, HardCopy III,

HardCopy IV, Stratix III, and Stratix IV devices only. When

you enable PLL calibration, you cannot merge the PLL with

other PLLs.

Use 'dpa_pll_recal' input port

This port recalibrates the PLL without resetting the DPA. This

option is available for Arria II GZ, HardCopy III, HardCopy

IV, Stratix III, and Stratix IV devices only.

What is the input data rate?

Specifies the data rate for the input channel of the receiver, in

Mbps. For data rate ranges, refer to the specific Device Data

Sheet chapter in the respective device handbook.

This value determines the legal input clock rate values.

Receiver Settings (page 8)

Register outputs

Turn on this option to implement soft-CDR receiver modes in

standard mode. In standard mode, the outputs of the receiver

are registered by the

rx_outclock

signal.

Turn off this option if you do not want to register the receiver

outputs. In no output register mode, you must register the

output registers in the design logic that is fed by the receiver,

and then specify a Source Multiply assignment from the

receiver to the output registers with a value equal to the

deserialization factor.

Use 'rx_cda_reset' input port

The port resets the data alignment circuitry, restoring the

latency bit counter to zero. This option is available only if you

turn on the Use 'rx_channel_data_align' input port option.

This option is available only if you use dedicated SERDES

block.

Use 'rx_cda_max' output port

Indicates when the rollover point is reached in the data

alignment circuit. This port is available only if you turn on the

Use 'rx_channel_data_align' input port option. This option is

available only if you use a a dedicated SERDES block.

After how many pulses does the data

alignment circuitry restore the serial

latency back to 0?

Specifies, in pulses, when the DPA circuitry restores the serial

data latency to 0.

The value does not have to be the same as the deserialization

factor, but set the value to the deserialization factor to make the

rollover occur for every deserialization factor.

The available values for this option range from 1 to 11. This

option is available only if you use a dedicated SERDES block.

UG-MF9504

2014.12.15

ALTLVDS_RX Parameter Settings

23

LVDS SERDES Transmitter/Receiver IP Cores User Guide

Altera Corporation