Altera LVDS SERDES Transmitter / Receiver User Manual

Page 70

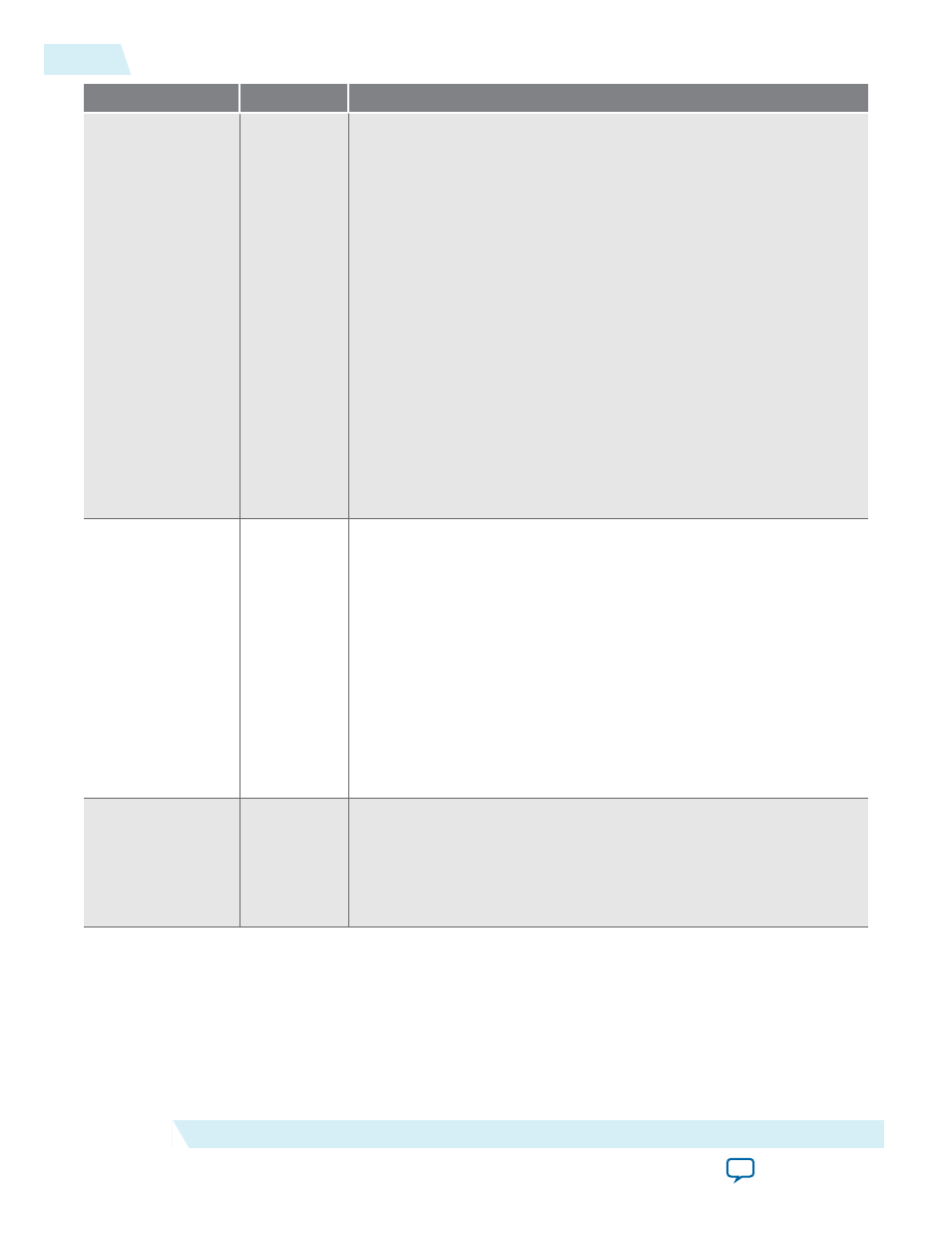

Date

Version

Changes

June 2013

2013.06.10 • Updated

on page 47 to add a note to recommend

using

rx_divfwdclk

(instead of any static clock) as the SignalTap

capturing clock.

• Updated

Receiver Skew Margin and Transmitter Channel-to-

on page 54to fix the error in RSKM equation by

replacing TCCS with RCCS. Also added information on how to

apply the RCCS figure to the RSKM calculation in TimeQuest.

• Updated

Arria II GX, Arria V, Arria V GZ, Cyclone V, and

Stratix V LVDS Package Skew Compensation Report Panel

on

page 61 to add Arria V, Arria V GZ, and Cyclone V devices.

• Updated

Figure 2

to fix the waveform error for c1 (288 degrees

phase shift)

• Updated

tx_enable

and

rx_enable ports

in

to clarify that the Set up PLL in LVDS mode option and the

enable0

and

enable1

ports are only for Stratix II devices.

• Updated

Parameters Used by the ALTPLL Megafunction

.

•

October 2012

v9.1

• Updated Table 2-2 on page 2-7 to fix content error for the What is

the deserialization factor? and Use 'rx_dpa_locked' output port

options.

• Updated "Clock Forwarding" on page 3-1.

• Updated "DPA PLL Calibration" on page 3-4 to fix device family

support.

• Updated "Dedicated SERDES" on page 3-9 to add a note on

TimeQuest Timing Analyzer.

• Updated Table 3-5 on page 3-25 to update description for rx_

in[]and rx_inclock.

• Updated Table 3-6 on page 3-28 to update description for tx_

inclock and tx_out[].

February 2012

v9.0

• Updated "Source-Synchronous Timing Analysis and Timing

Constraints" section.

• Added design examples.

• Updated "Parameter Settings" chapter to include "Use Clock Pin"

parameter.

70

Document Revision History

UG-MF9504

2014.12.15

Altera Corporation

LVDS SERDES Transmitter/Receiver IP Cores User Guide