Altera LVDS SERDES Transmitter / Receiver User Manual

Page 29

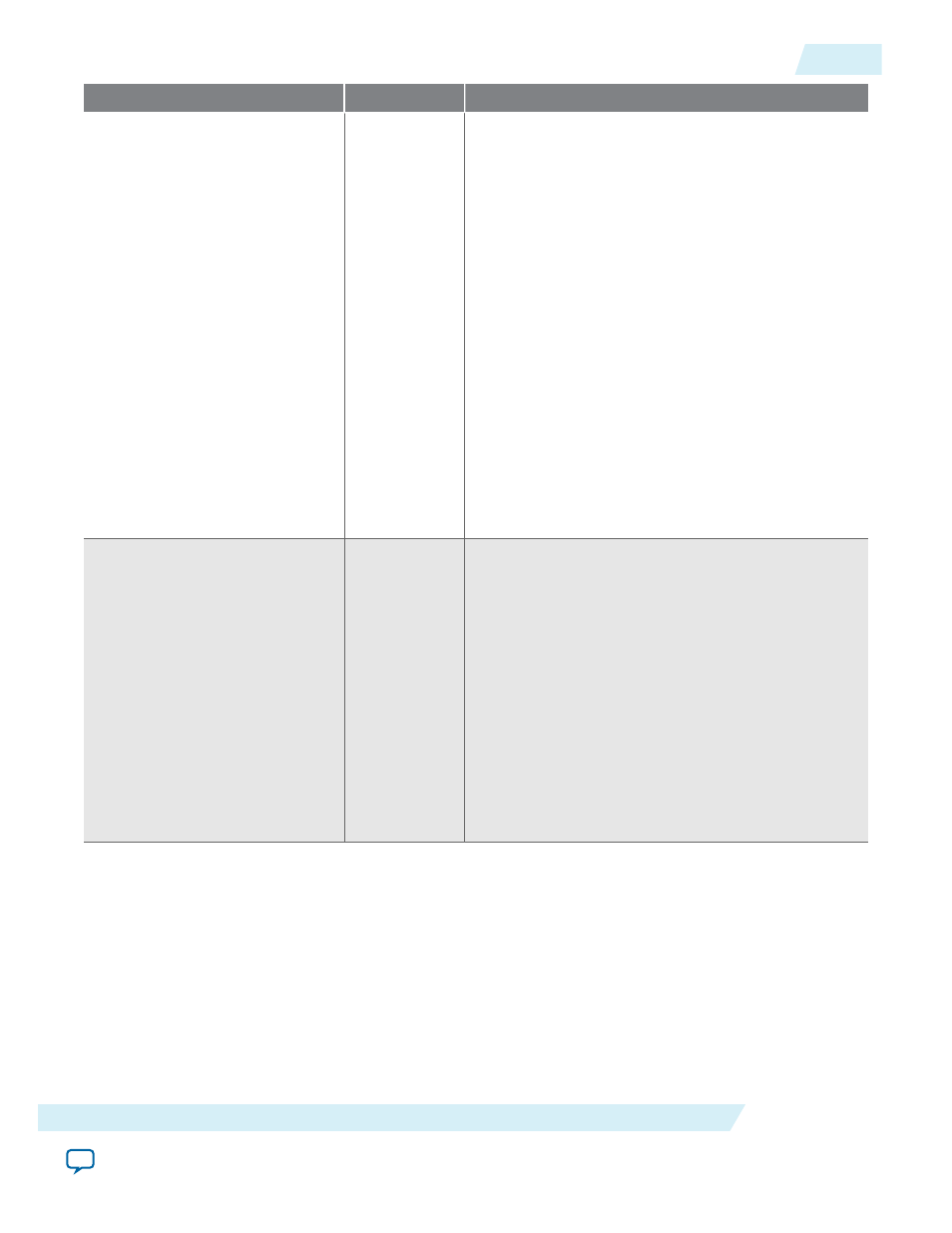

Parameter

Type

Description

outclock_alignment

String

Specifies the alignment of

tx_outclock

with respect

to the VCO of a fast PLL. The clock phase alignment

for the

outclock_alignment

parameter is data

leading.

This parameter is only used by the RTL simulation

model and has no affect on how the Fitter sets the

PLL parameters.

Values are:

•

EDGE_ALIGNED: 0°

•

45_DEGREES: 45°

•

90_DEGREES: 90°

•

135_DEGREES: 135°

•

CENTER_ALIGNED:180°

•

225_DEGREES: 225°

•

270_DEGREES: 270°

•

315_DEGREES: 315°

If omitted, the default value is

EDGE_ALIGNED

.

Available for all devices excluding the MAX series.

outclock_divide_by

Integer

Specifies the period of the

tx_outclock

port as

[INCLOCK_PERIOD * OUTCLOCK_DIVIDE_BY]

and the

frequency of the

tx_outclock

port as

[INCLOCK_

PERIOD/OUTCLOCK_DIVIDE_BY]

. The default value for

this parameter is the value of the

deserialization_

factor

parameter.

Only available for Arria GX, Arria II GX, Arria II GZ,

Arria V, Arria V GZ, Cyclone, Cyclone II, Cyclone

III, Cyclone IV, HardCopy II, HardCopy III,

HardCopy IV, Stratix, Stratix GX, Stratix II, Stratix II

GX, Stratix III, Stratix IV, and Stratix V devices.

For more information about the

DESERIALIZATION_

FACTOR

and

outclock_divide_by

values, refer to

.

UG-MF9504

2014.12.15

Command Line Interface Parameters

29

LVDS SERDES Transmitter/Receiver IP Cores User Guide

Altera Corporation