Altera LVDS SERDES Transmitter / Receiver User Manual

Page 25

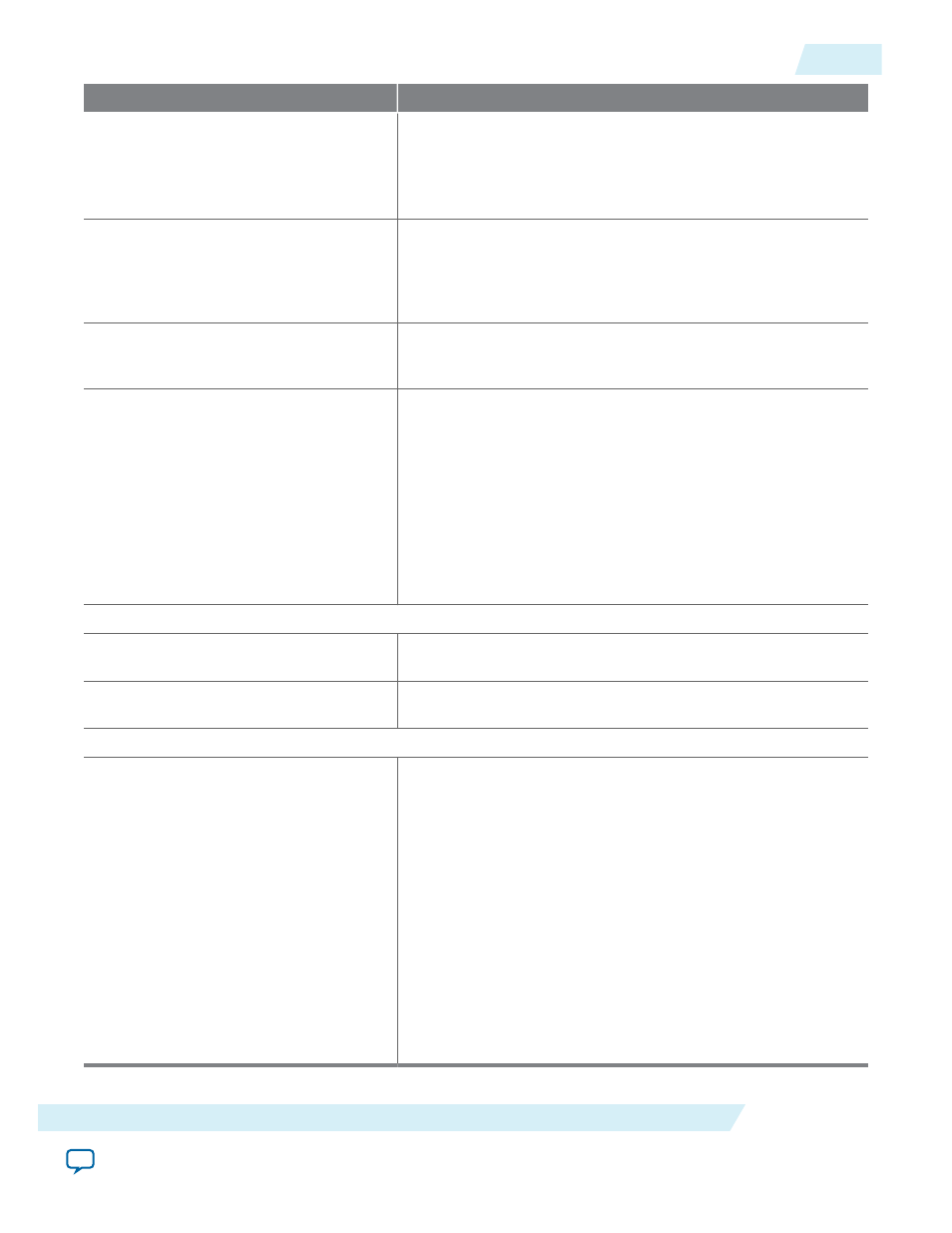

Option

Description

Enable independent bitslip controls for

each channel

Turn on this option to allow an independent

rx_data_align

signal for each channel that independently control the bit slip

capability of each channel.

This option is available if you implement the SERDES in LEs.

Add extra register for 'rx_data_align'

input port

Turn on this option to enable the synchronization register of

the receiver. If you turn on this option, you can also add an

extra register to register the

rx_data_align

port using the

rx_

outclock

port. This option is available if you implement the

SERDES in LEs.

Use 'rx_data_align_reset' input port

Turn on this option to create the reset port for the bit-slip

circuitry. This option is available if you implement the SERDES

in LEs.

Which output synchronization buffer

implementation should be used?

Specifies where to implement the buffer. The values are Use

RAM Buffer, Use Multiplexer and synchronization register,

and Use logic element based RAM buffer. A value of Use

Multiplexer and synchronization register implements a

multiplexer instead of a buffer. A value of Use RAM Buffer

implements a buffer in RAM blocks. A value of Use logic

element based RAM buffer implements a buffer in logic

elements. The Use RAM Buffer and Use logic element based

RAM buffer values use more logic, but result in the correct

word alignment. If omitted, the default value is Use RAM

Buffer.

Simulation Model (page 9)

Simulation Libraries

Specifies the libraries needed for functional simulation by

third-party tools.

Generate netlist

Turn on this option to generate synthesis area and timing

estimation netlist.

Summary (page 10)

Summary

Specifies the types of files to be generated. A gray checkmark

indicates a file that is automatically generated; a green

checkmark indicates an optional file.

Choose from the following types of files:

• AHDL Include file (<function name>.inc)

• VHDL component declaration file (<function name>.cmp)

• Quartus II symbol file (<function name>.bsf)

• Instantiation template file (<function name>_inst.v or

<function name>_inst.vhd

• Verilog HDL block box file (<function name>_bb.v)

• Pin Planner File (<function name>_.ppf)

If you turn on the Generate netlist option, the file for that

netlist is also available (<function name>_syn.v).

UG-MF9504

2014.12.15

ALTLVDS_RX Parameter Settings

25

LVDS SERDES Transmitter/Receiver IP Cores User Guide

Altera Corporation