Ports, Altlvds_tx ports – Altera LVDS SERDES Transmitter / Receiver User Manual

Page 40

Ports

This section describes the ports for the ALTLVDS_TX and ALTLVDS_RX IP cores.

ALTLVDS_TX Ports

The following table lists the input and output ports for the ALTLVDS_TX IP core.

n is the number of channels. m is the

deserialization_factor

×

number_of_channels

.

Note: If you use dedicated SERDES, regardless of device family, you do not need to make additional

constraints on the data port.

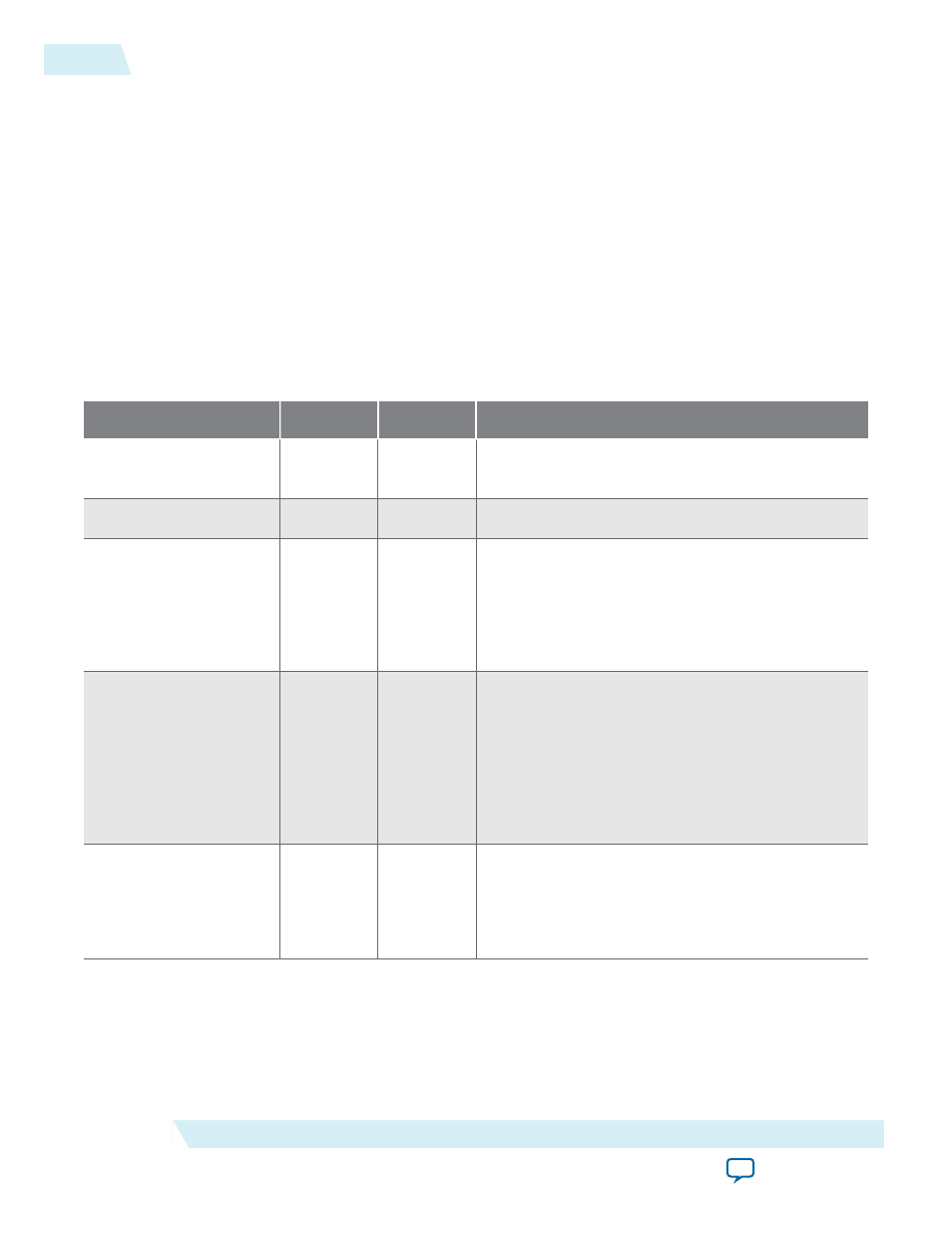

Table 10: ALTLVDS_TX Input and Output Ports

For Stratix IV, Arria II, and Cyclone IV devices, use the ALTPLL IP core. For Stratix V, Arria V, and Cyclone V

devices use the Altera PLL IP core.

Port Name

Direction

Width (Bit)

Description

pll_areset

Input

1

Asynchronously resets all counters to the initial

values.

sync_inclock

Input

1

Optional clock for the input registers.

tx_data_reset

Input

n

Asynchronous reset for the shift registers, capture

registers, and synchronization registers for all

channels. This port is available only when

implement_in_les

parameter is set to

ON

. This port

does not affect the data realignment block or the

PLL.

tx_enable

Input

1

Enables external PLL usage.

When the

tx_enable

port is specified, connect the

port to the

enable0

or

enable1

port of a PLL IP

core instance.

However, the

enable0

,

enable1

ports and the Set

up PLL in LVDS mode option are available for

Stratix II devices only.

tx_in[]

Input

m

This is parallel data which needs to be serially

transmitted by the IP core. Input data must be

synchronous to the

tx_coreclock

signal. The data

bus width per channel is the same as the serializa‐

tion factor (SF)

40

Ports

UG-MF9504

2014.12.15

Altera Corporation

LVDS SERDES Transmitter/Receiver IP Cores User Guide