Altlvds ip core in external pll mode – Altera LVDS SERDES Transmitter / Receiver User Manual

Page 62

The Recommended Trace Delay Addition column in the report panel displays the recommended

amount of trace delay that you must add to each trace of the corresponding LVDS pins, which reduces the

channel-to-channel skew between the LVDS channels. For example, in

delay addition for

pin_name7

[0] is 67 ps. This means you must manually adjust the PCB trace for

pin_name7[0]

to have a delay addition of 67 ps. The corresponding pin is listed in the Pin column, in the

report panel.

The report panel also shows the total estimated TCCS and SW reductions when the recommended trace

delay values are added to the PCB trace.

ALTLVDS IP Core in External PLL Mode

PLL Clock Signals for LVDS Interface in External PLL Mode

The parameter editor provides the Use External PLL option. This option allows you to control PLL

settings to support different data rates, dynamic phase shift, and other settings. In external PLL mode, you

must instantiate a PLL IP core to generate the various clock and load enable signals.

Note: For Stratix IV, Arria II, and Cyclone IV devices, use the ALTPLL IP core. For Stratix V, Arria V,

and Cyclone V devices use the Altera PLL IP core.

If you enable the Use External PLL option, you require the following signals from the PLL IP core:

• Serial clock input to the SERDES of the ALTLVDS transmitter and receiver.

• Load enable to the SERDES of the ALTLVDS transmitter and receiver.

• Parallel clock to clock the transmitter FPGA fabric logic.

• Parallel clock for the receiver

rx_syncclock

port and receiver FPGA fabric logic.

• Asynchronous PLL reset port of the ALTLVDS receiver.

Generate the serial clock output, load enable output, and the parallel clock output on ports

c0

,

c1

, and

c2

,

along with the locked signal of the PLL IP core instance. You can choose any of the PLL output clock

ports to generate the interface clocks.

Note: The high-speed clock generated from the PLL is for clocking the LVDS SERDES circuitry only. Do

not use the high-speed clock to drive other logic because the allowed frequency to drive the core

logic is restricted by the PLL FOUT specification.

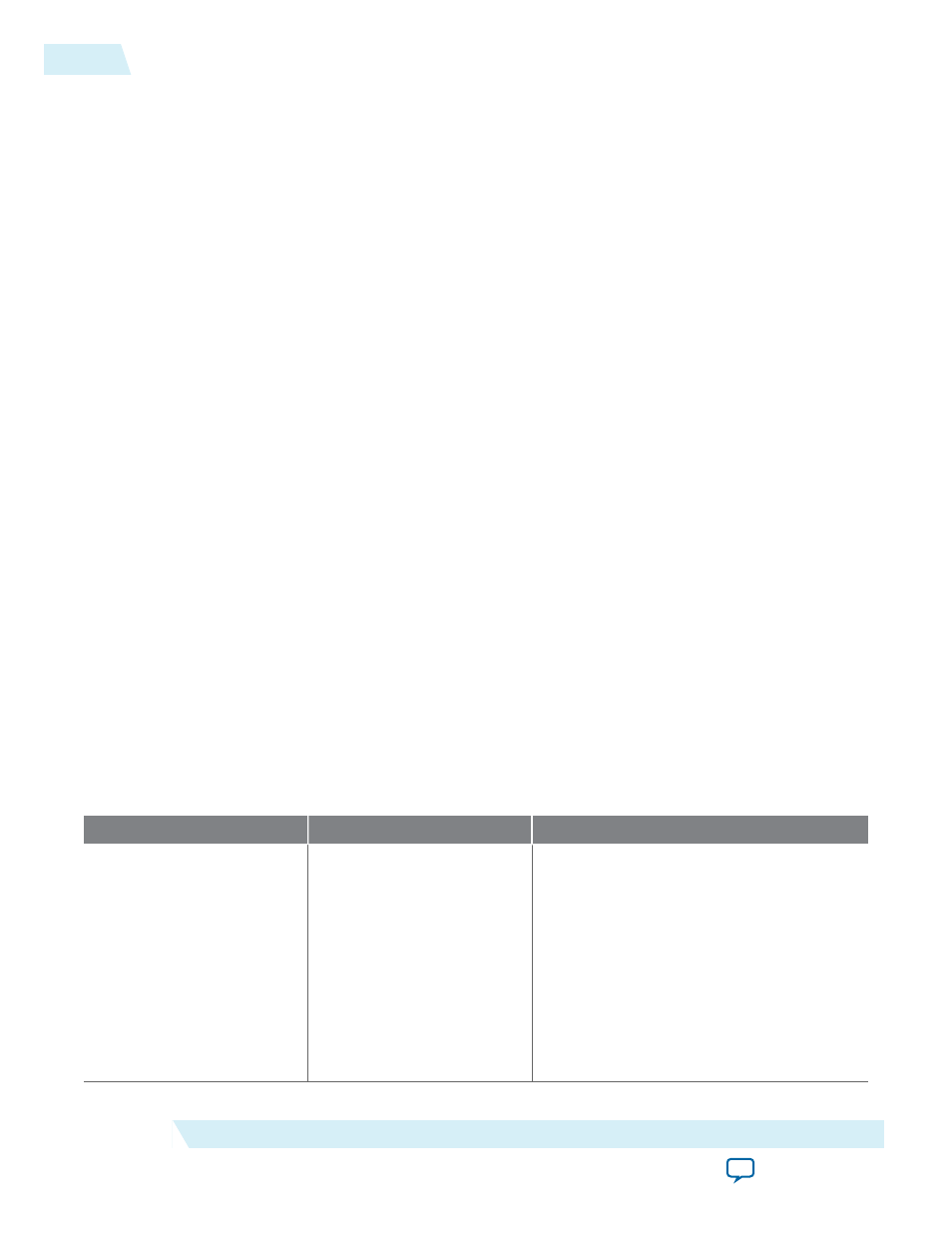

Table 13: Signal Interface Between PLL IP Core and ALTLVDS IP Core

This table lists the signal interface between the output ports of the PLL IP core and the input ports of the

ALTLVDS transmitter and receiver.

From the PLL

To the ALTLVDS Transmitter

To the ALTLVDS Receiver

Serial clock output (c0)

Note: The serial clock

output (c0) can

only drive

tx_

inclock

on the

ALTLVDS

transmitter and

rx_

inclock

on the

ALTLVDS receiver.

This clock cannot

drive the core logic.

tx_inclock

(serial clock input

to the transmitter)

rx_inclock

(serial clock input)

62

ALTLVDS IP Core in External PLL Mode

UG-MF9504

2014.12.15

Altera Corporation

LVDS SERDES Transmitter/Receiver IP Cores User Guide