Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 10

1–6

Chapter 1: About This Compiler

Performance and Resource Utilization

POS-PHY Level 2 and 3 Compiler User Guide

© November 2009

Altera Corporation

Preliminary

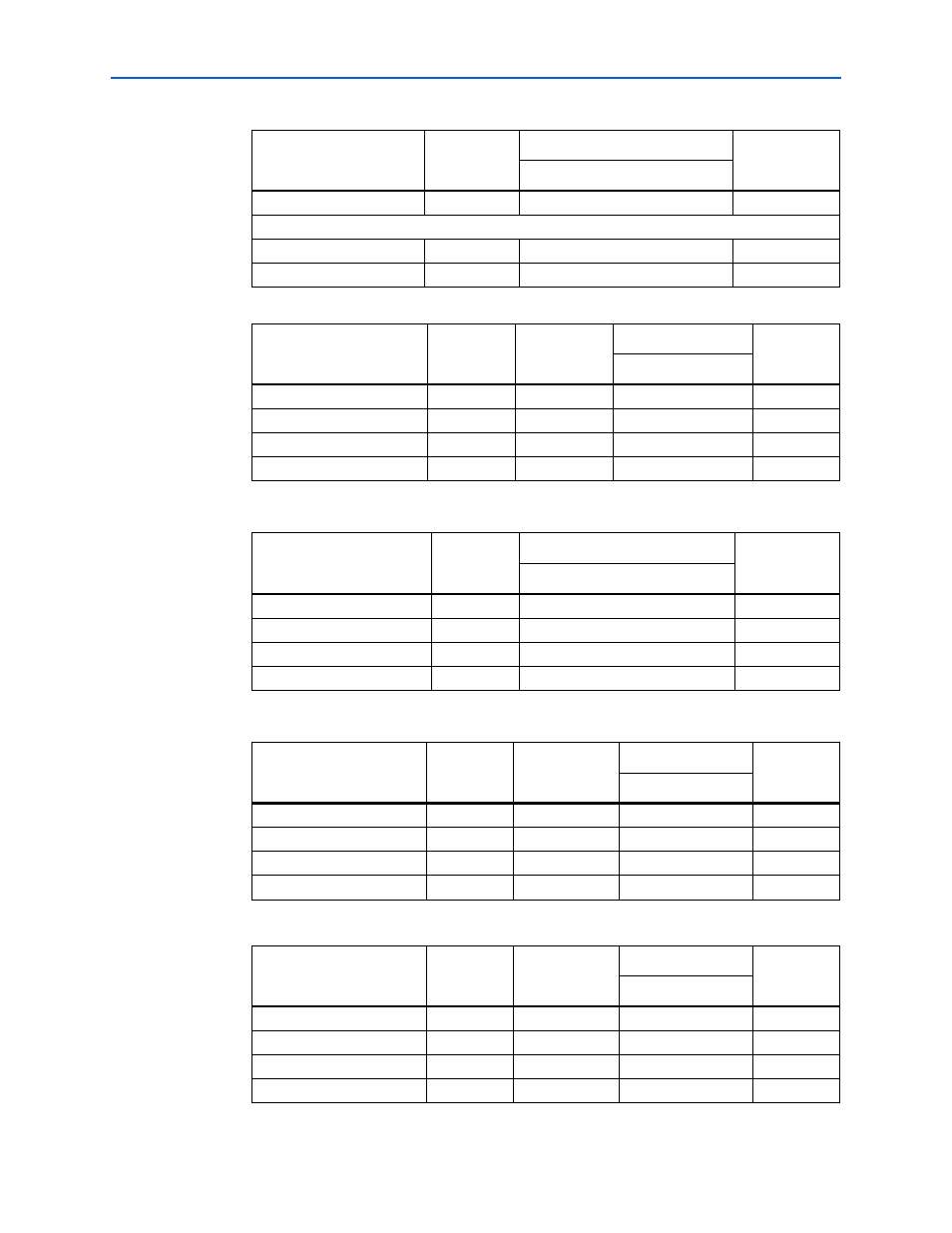

SPHY transmit

285

2

159

Device: EP2C15AF484C6

MPHY 4-port receive

1,175

8

161

MPHY 4-port transmit

1,126

8

139

Table 1–6. Performance—POS-PHY Level 2 PHY Layer—Stratix III Device

MegaCore Function

ALUTs

Logic

Registers

Memory Blocks

f

MAX

(MHz)

M9K

SPHY receive

122

309

2

340

SPHY transmit

123

234

2

346

MPHY 4-port receive

487

995

8

318

MPHY 4-port transmit

529

918

8

293

Table 1–7. Performance—POS-PHY Level 3 Link Layer—Cyclone III Device

MegaCore Function

LEs

Memory Blocks

f

MAX

(MHz)

M9K

SPHY receive

379

2

165

SPHY transmit

377

2

139

MPHY 4-port receive

1,202

8

171

MPHY 4-port transmit

1,242

8

164

Table 1–8. Performance—POS-PHY Level 3 Link Layer—Stratix III Device

MegaCore Function

ALUTs

Logic

Registers

Memory Blocks

f

MAX

(MHz)

M9K

SPHY receive

149

330

2

234

SPHY transmit

164

313

2

205

MPHY 4-port receive

522

1,019

8

217

MPHY 4-port transmit

613

1,009

8

178

Table 1–9. Performance—POS-PHY Level 3 Link Layer—Stratix IV Device

MegaCore Function

ALUTs

Logic

Registers

Memory Blocks

f

MAX

(MHz)

M9K

SPHY receive

149

330

2

231

SPHY transmit

164

313

2

180

MPHY 4-port receive

522

1,019

8

254

MPHY 4-port transmit

613

1,009

8

174

Table 1–5. Performance—POS-PHY Level 2 PHY Layer—Cyclone II Device (Part 2 of 2)

MegaCore Function

LEs

Memory Blocks

f

MAX

(MHz)

M4K