Internal architecture, Internal architecture –4, Pos-phy level 2 link-layer – Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 32: Pos-phy level 2 phy-layer, Pos-phy level 3 link-layer, Pos-phy level 3 phy-layer, Figure 3–7. example implementation, Figure 3–8. example implementation 2

3–4

Chapter 3: Functional Description

Internal Architecture

POS-PHY Level 2 and 3 Compiler User Guide

© November 2009

Altera Corporation

Preliminary

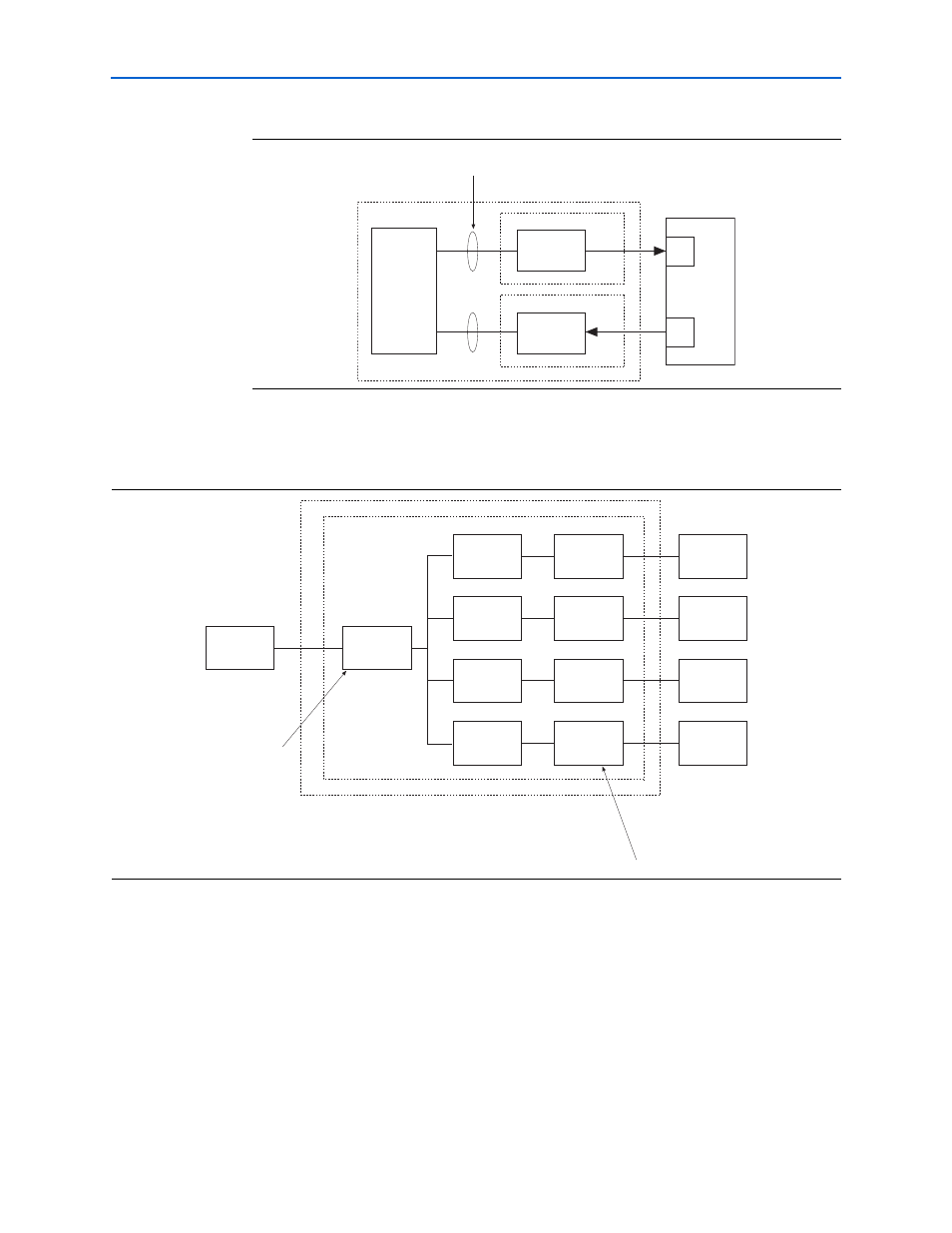

Figure 3–8 on page 3–4

shows the FPGA interfacing multiple POS-PHY level 2 devices

to an OC-48 switch.

Internal Architecture

The POS-PHY Level 2 and 3 Compiler comprises the following four MegaCore

functions:

■

POS-PHY level 2 link-layer

■

POS-PHY level 2 PHY-layer

■

POS-PHY level 3 link-layer

■

POS-PHY level 3 PHY-layer

Figure 3–7. Example Implementation

Level 3 Link

Interface

(Source)

Level 3 Link

Interface

(Sink)

OC48 Framer

User Logic

FPGA

MegaCore Function 1

MegaCore Function 1

PHY

PHY

Atlantic

Interfaces

Figure 3–8. Example Implementation 2

OC48

Switch

(Link)

Level 3

PHY

Interface

FIFO

FIFO

FIFO

Level 2

PHY Device

Level 2

PHY Device

Level 2

PHY Device

FIFO

Level 2

Link

Interface

Level 2

Link

Interface

Level 2

Link

Interface

Level 2

Link

Interface

Level 2

PHY Device

FPGA

MegaCore Function

'A' Interface

'B' Interface