Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 47

Chapter 3: Functional Description

3–19

Interface Signals

© November 2009

Altera Corporation

POS-PHY Level 2 and 3 Compiler User Guide

Preliminary

Table 3–10

describes the POS-PHY level 3 receive interface.

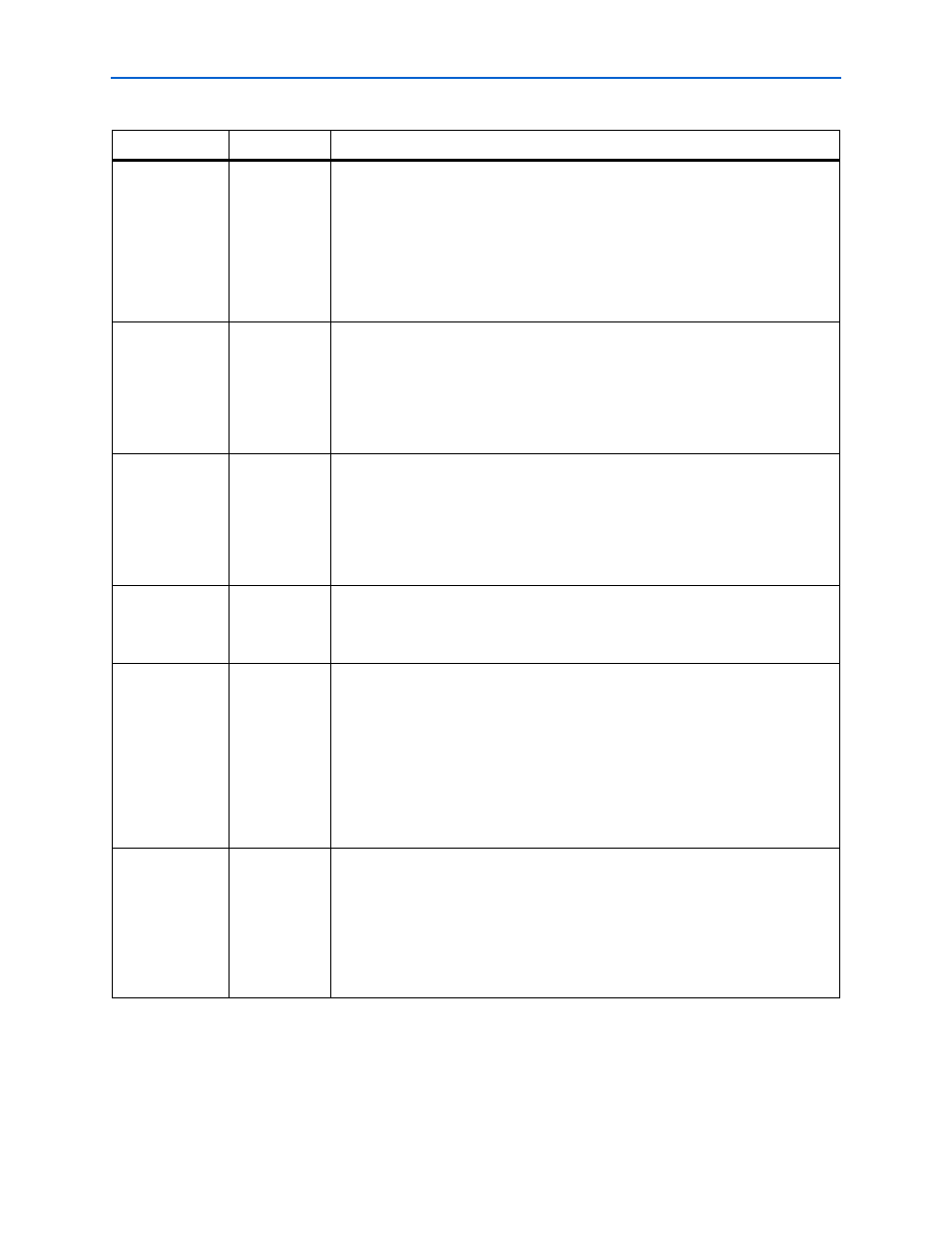

tenb

Link to PHY

Transmit write enable. tenb controls the flow of data to the transmit FIFO buffers.

When tenb is high, tdat, tmod, tsop, teop and terr are invalid and are

ignored by the PHY-layer. The tsx signal is valid and is processed by the PHY when

tenb

is high. When tenb is low, tdat, tmod, tsop, teop and terr are valid

and are processed by the PHY-layer. Also, the tsx signal is ignored by the PHY-layer,

when tenb is low.

If you choose Atlantic master for the ‘B’ interface, the tenb signal is combinational.

tsx

Link to PHY

Transmit start of transfer signal. tsx indicates when the in-band port address is

present on the tdat bus. When tsx is high and tenb is high, the value of

tdat[7:0]

is the address of the transmit FIFO buffer to be selected. Subsequent

data transfers on the tdat bus fill the FIFO buffer specified by this in-band address.

For single-port PHY devices, the tsx signal is optional, because the PHY device

ignores in-band addresses when tenb is high. tsx is valid only when tenb is not

asserted.

dtpa[]

PHY to link

Byte-level

mode

Direct transmit packet available. dtpa provides status indication of the

corresponding port in the PHY device. dtpa asserts high when a predefined (user

programmable) minimum number of bytes is available in the transmit FIFO buffer.

dtpa

high does not indicate that the transmit FIFO buffer is full. When dtpa

transitions low, it indicates that its transmit FIFO buffer is full or nearly full (user

programmable). dtpa is required if byte-level transfer mode is supported. dtpa is

updated on the rising edge of tfclk.

tadr[]

(1)

Link to PHY

Transmit address. tadr is used with ptpa to poll the transmit FIFO buffer's packet

available status. When tadr is sampled on the rising edge of tfclk by the PHY, the

polled packet available indication ptpa is updated with the status of the port

specified by the tadr address on the following rising edge of tfclk.

stpa

(2)

PHY to link

Selected PHY transmit packet available. stpa transitions high, when

fifo_threshold

words are available in the transmit FIFO buffer specified by the

in-band address on tdat. When high, stpa indicates that the transmit FIFO buffer is

not full. When stpa transitions low, it indicates that the transmit FIFO buffer is full or

near full (user programmable). stpa always provides status indication for the

selected port of the PHY device to avoid FIFO buffer overflows while polling is

performed. The port which stpa reports is updated on the following rising clock

edge of tfclk after the PHY address on tdat is sampled by the PHY device. stpa

is required if byte-level transfer mode is supported. stpa is updated on the rising

edge of tfclk.

ptpa

(1)

PHY to link

Polled PHY transmit packet available. ptpa transitions high when

fifo_threshold

words are available in the polled transmit FIFO buffer. When

high, ptpa indicates that the transmit FIFO buffer is not full. When ptpa transitions

low, it indicates that the transmit FIFO buffer is full or near full (user programmable).

ptpa

allows the polling of the PHY selected by the tadr address bus. The port that

ptpa

reports is updated on the following rising edge of tfclk, after the PHY

address on tadr is sampled by the PHY device. ptpa is required if packet-level

transfer mode is supported. ptpa is updated on the rising edge of tfclk.

Notes to

Table 3–9

:

(1) Packet-level mode only

(2) Byte-level mode only

Table 3–9. POS-PHY Level 3 Transmit Interface (Part 2 of 2)

Signal

Direction

Description