Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 26

2–14

Chapter 2: Getting Started

Simulate the Design

POS-PHY Level 2 and 3 Compiler User Guide

© November 2009

Altera Corporation

Preliminary

3. Add the following files to the project from the \posphy_l2_l3\lib directory:

■

auk_pac_gen_if.vhd

■

auk_pac_functions.vhd

■

auk_pac_components.vhd

The files must be in the order shown, from top to bottom, which is the order of

compilation. Use the Up and Down buttons in the New Project Wizard: Add Files

window to order the files.

4. Check that the absolute path to your third-party simulation tool is set. Set the path

from EDA Tool Options in the Options dialog box (Tools menu).

5. On the Processing menu, point to Start and click Start Analysis & Elaboration.

1

If the analysis and elaboration is not successful, fix the error before moving

to the next step.

6. On the Assignments menu, click Settings. The Settings window appears. Expand

EDA Tool Settings

and select Simulation.

7. In Tool name, select a simulator tool from the list.

In EDA Netlist Writer options, select Verilog from the list for Format for output

netlist

(Select VHDL if you are preparing a VHDL simulation).

In NativeLink settings, select the Compile test bench option and then click Test

Benches

. The Test Benches window appears.

8. In the Test Benches window, click New. The New Test Bench Settings window

appears.

9. In the New Test Bench Settings window, enter the information described in

Table 2–2

(see also

Figure 2–16 on page 2–15

). To enter the files described in the

table, browse to the files in your project.

Figure 2–16

shows the testbench settings for a receive simulation.

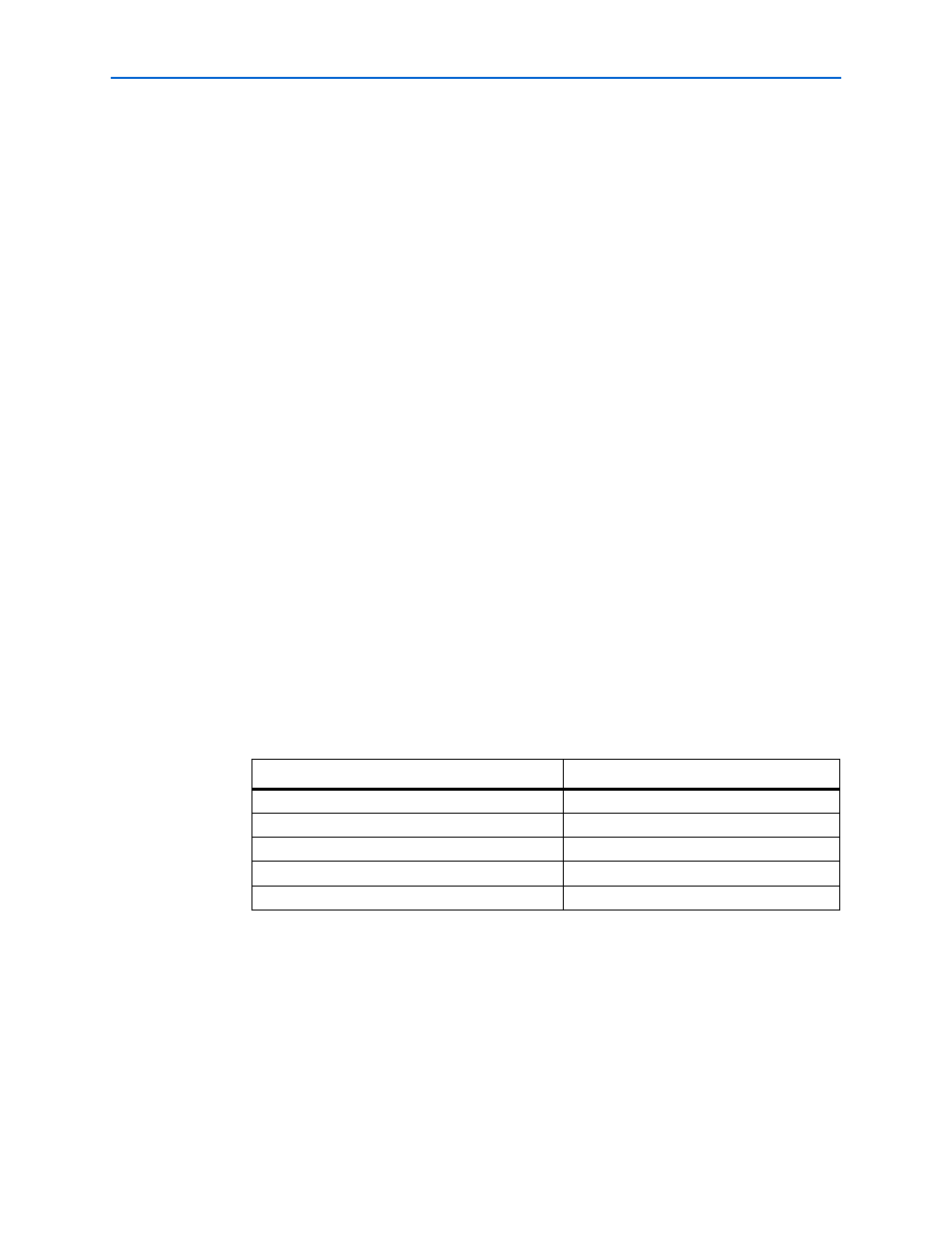

Table 2–2. NativeLink Test Bench Settings

Parameter

Setting/File Name

Test bench name

<any name>

Top-level module in test bench

auk_pac_mrx_ref

Design instance name in test bench

Run for

100 ns

Test bench files

auk_pac_mrx_ref_tb.v

Notes to table:

(1) Use mtx for Tx simulations.

(2) If you are preparing a VHDL simulation, use auk_pac_mrx_ref_tb.vhd in the vhdl directory.