Example implementations, Example implementations –3 – Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 31

Chapter 3: Functional Description

3–3

Example Implementations

© November 2009

Altera Corporation

POS-PHY Level 2 and 3 Compiler User Guide

Preliminary

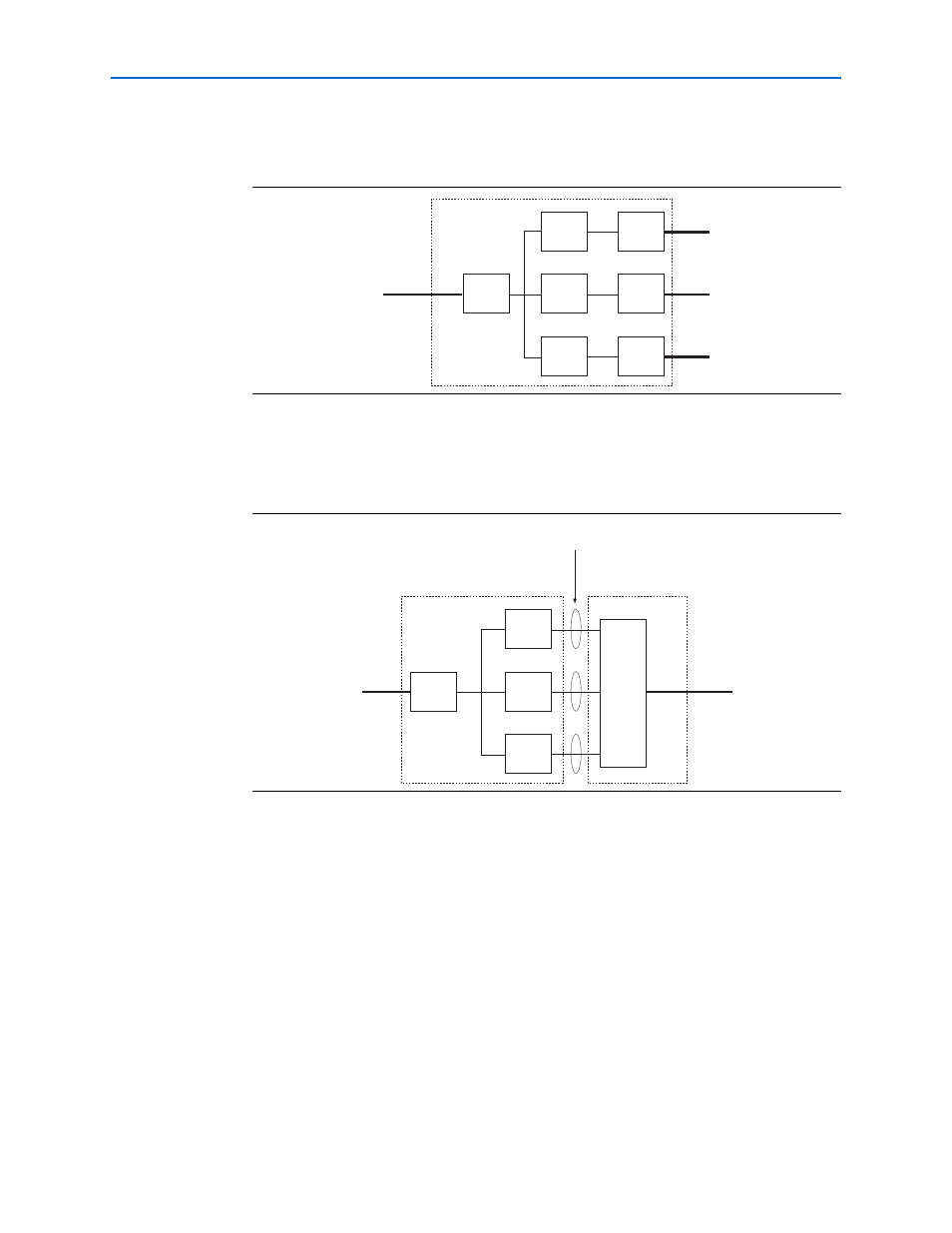

Figure 3–5

shows a bridging function with multiple lower-rate ports, which can be 8-

bit POS-PHY level 3 or 16-bit POS-PHY level 2.

Figure 3–6 on page 3–3

shows an MPHY to MPHY POS-PHY bridge, which includes

an MPHY POS-PHY level 2 interface and one first-in first-out (FIFO) buffer per

supported address (MPHY).

Example Implementations

Figure 3–7

shows the FPGA interfacing to an OC-48 framer.

Figure 3–5. Example Configuration 2—POS-PHY Bridging Functions

Figure 3–6. Example Configuration 3—MPHY to MPHY Bridge

Level 3

Link

Interface

FIFO

FIFO

FIFO

Level 2

PHY

Interface

MegaCore Function 1

100 MHz

32 bit

50 MHz

16 bit

Level 2

PHY

Interface

50 MHz

16 bit

Level 3

PHY

Interface

100 MHz

8 bit

Level 3

PHY

Interface

FIFO

FIFO

FIFO

Level 2

Link

Interface

Atlantic

Interfaces

MegaCore Function 1

MegaCore Function 2

100 MHz

8 bit

50 MHz

16 bit