Simulate the design, Simulate the design –12 – Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 24

2–12

Chapter 2: Getting Started

Simulate the Design

POS-PHY Level 2 and 3 Compiler User Guide

© November 2009

Altera Corporation

Preliminary

2. After you review the generation report, click Exit to close IP Toolbench and click

Yes

on the Quartus II IP Files message.

1

The Quartus II IP File (.qip) is a file generated by the MegaWizard interface or SOPC

Builder that contains information about a generated IP core. You are prompted to add

this .qip file to the current Quartus II project at the time of file generation. In most

cases, the .qip file contains all of the necessary assignments and information required

to process the core or system in the Quartus II compiler. Generally, a single .qip file is

generated for each MegaCore function and for each SOPC Builder system. However,

some more complex SOPC Builder components generate a separate .qip file, so the

system .qip file references the component .qip file.

You can now integrate your custom MegaCore function variation into your design,

simulate, and compile.

Simulate the Design

You can simulate your design using the IP Toolbench-generated VHDL and Verilog

HDL IP functional simulation models.

f

For more information on IP functional simulation models, refer to

Simulation Model” on page 2–13

me 3 of the Quartus II Handbook.

Altera also provides fixed example VHDL and Verilog HDL testbenches that you can

use to simulate example sink or source POS-PHY systems. You can use a testbench as

a basis for your own design. The testbenches can be used with the IP functional

simulation models. The testbenches and associated files are located in the

sim_lib\testbench directory.

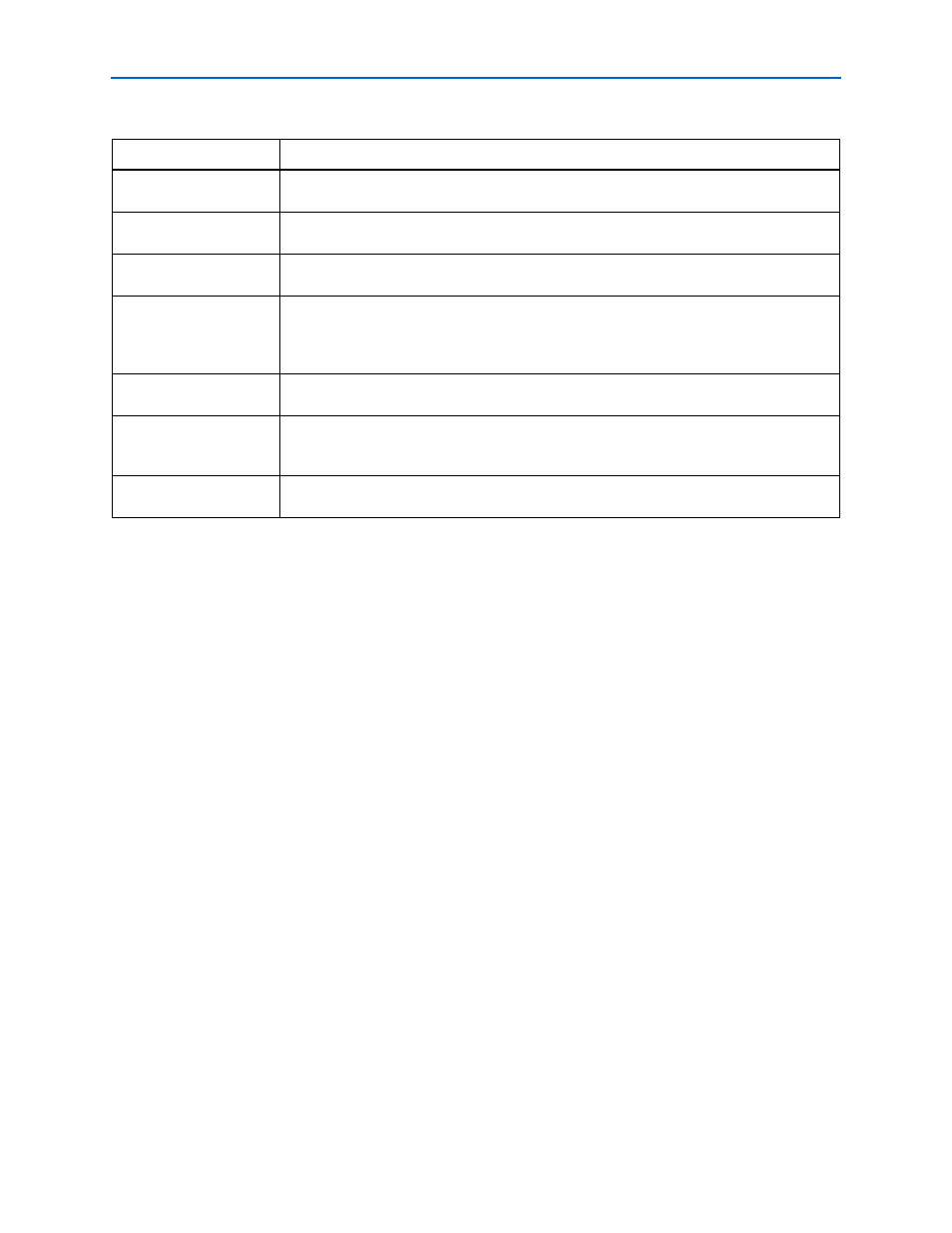

Table 2–1. Generated Files

Extension

Description

<

variation name>syn.v or

<

variation name>syn.vhd

A timing and resource netlist for use in some third-party synthesis tools.

<

variation name>.bsf

Quartus II symbol file for the MegaCore function variation. You can use this file in the

Quartus II block diagram editor.

<

variation name>.cmp

A VHDL component declaration file for the MegaCore function variation. Add the contents of

this file to any VHDL architecture that instantiates the MegaCore function.

<variation name>.ppf

This XML file describes the MegaCore function pin attributes to the Quartus II Pin Planner.

MegaCore function pin attributes include pin direction, location, I/O standard assignments, and

drive strength. If you launch IP Toolbench outside of the Pin Planner application, you must

explicitly load this file to use Pin Planner.

<variation name>.ppx

This XML file is a Pin Planner support file that Pin Planner automatically uses. This file must

remain in the same directory as the <variation name>.ppf file.

<variation name>.vhd or

<variation name>.v

A MegaCore function variation file, which defines a VHDL or Verilog HDL top-level description

of the custom MegaCore function. Instantiate the entity defined by this file inside your design.

Include this file when compiling your design in the Quartus II software.

<variation name>.vo or

<variation name>.vho

VHDL or Verilog HDL IP functional simulation model.