Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 39

Chapter 3: Functional Description

3–11

Parameters

© November 2009

Altera Corporation

POS-PHY Level 2 and 3 Compiler User Guide

Preliminary

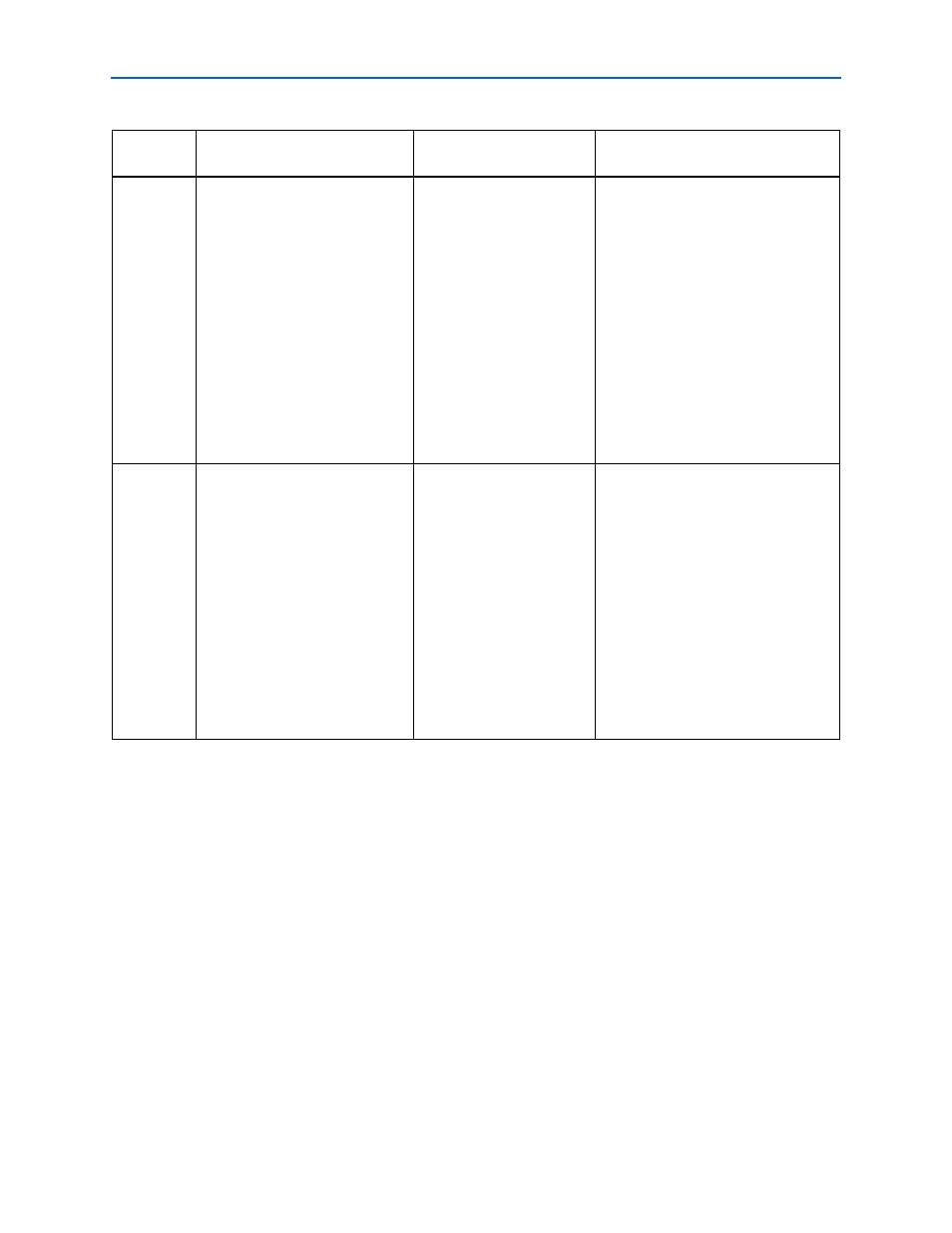

Table 3–4

shows the effect of the FIFO buffer settings for POS-PHY level 2 interfaces.

PHY

Transmit

(Sink)

When there is more than or equal

to FIFO buffer threshold spaces for

bytes in any of its FIFO buffers (1

FIFO buffer per channel), the

interface indicates this on a per

channel basis to the link transmit

interface.

When operating in polled mode,

this is indicated by asserting PTPA

and STPA outputs.

When operating in direct status

mode, this is indicated by asserting

the DTPA outputs.

When there is less than FIFO

buffer burst spaces for bytes

in any of its FIFO buffers (1

FIFO buffer per channel), the

interface indicates this on a

per channel basis to the link

transmit interface.

When operating in polled

mode, this is indicated by

deasserting the PTPA and

STPA outputs.

When operating in direct

status mode, this is indicated

by deasserting the DTPA

outputs.

—

PHY

Receive

(Source)

When each FIFO buffer fills to

above the FIFO buffer threshold

level, or contains a packet or

packet fragment with an EOP, it

triggers its not empty flag. The

interface then tries to empty each

of the FIFO buffers with data, as

soon as it detects the link receive

interface has asserted low the

RENB input.

Indicates the maximum

number of bytes the interface

transfers in each FIFO buffer

burst.

In MPHY mode, at the end of

each FIFO buffer burst the

MegaCore function re-

arbitrates for a new channel

in a round-robin fashion.

Set FIFO buffer burst <= FIFO

buffer threshold.

In SPHY mode, this should

be set to the minimum value

allowed.

—

Table 3–3. POS-PHY Level 3 FIFO Buffer Settings (Part 2 of 2)

Interface

(Direction)

FIFO Threshold

FIFO Burst

FIFO Remote Burst