Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 46

3–18

Chapter 3: Functional Description

Interface Signals

POS-PHY Level 2 and 3 Compiler User Guide

© November 2009

Altera Corporation

Preliminary

■

Link to PHY results in an output port on the MegaCore function.

■

PHY to link results in an input port on the MegaCore function.

For a POS-PHY level 3 PHY-layer MegaCore function, the following rules apply:

■

Link to PHY results in an input port on the MegaCore function.

■

PHY to link results in an output port on the MegaCore function.

1

‘A’ interface signals are prefixed by a_; ‘B’ interface signals are prefixed by b1_, b2_,

and so on.

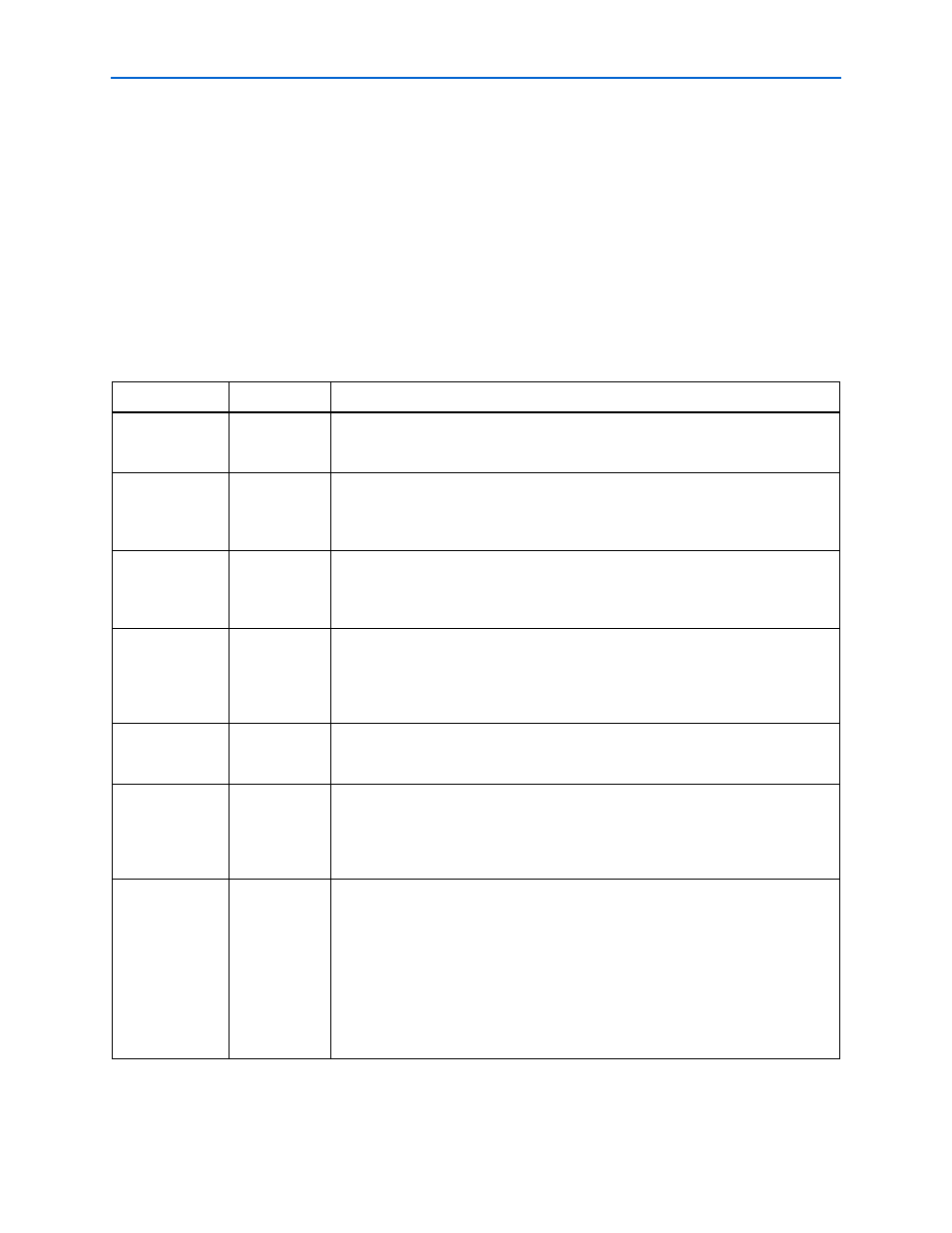

Table 3–9

describes the POS-PHY level 3 transmit interface.

Table 3–9. POS-PHY Level 3 Transmit Interface (Part 1 of 2)

Signal

Direction

Description

tfclk

Input

Transmit FIFO buffer write clock. tfclk synchronizes data transfer transactions

between the link-layer device and the PHY-layer device. tfclk can cycle at a rate up

to 104 MHz.

tdat[31:0]

Link to PHY

Transmit packet data bus. This bus carries the packet octets that are written to the

selected transmit FIFO buffer. The tdat bus is valid only when tenb is asserted.

The data must be transmitted in big-endian order on tdat. When an 8-bit interface is

used, only tdat[7:0] is supported.

tsop

Link to PHY

Transmit start of packet signal. tsop delineates the packet boundaries on the tdat

bus. When tsop is high, the start of the packet is present on the tdat bus. tsop is

required to be present at the beginning of every packet and is valid only when tenb is

asserted.

teop

Link to PHY

Transmit end of packet signal. teop delineates the packet boundaries on the tdat

bus. When teop is high, the end of the packet is present on the tdat bus. tmod

indicates the number of valid bytes the last double-word is composed of, when teop

is asserted. teop is required to be present at the end of every packet and is valid only

when tenb is asserted.

terr

Link to PHY

Transmit error indicator signal. terr indicates that the current packet should be

aborted. When terr is set high, the current packet is aborted. terr should only be

asserted when teop is asserted.

tprty

Link to PHY

Transmit bus parity signal. The transmit parity signal indicates the parity calculated

over the tdat bus. tprty is valid only when tenb is asserted. When tprty is

supported, the PHY-layer device must support both even and odd parity. The PHY-

layer device must report any parity error to higher layers, but does not interfere with

the transferred data.

tmod[1:0]

Link to PHY

Transmit word modulo. tmod indicates the number of valid data bytes in tdat. The

tmod

bus is normally zero, except during the last double-word transfer of a packet on

tdat

. When teop is asserted, the number of valid packet data bytes on tdat is

specified by tmod.

When tmod[1:0] = ‘00’, tdat[31:0] is valid.

When tmod[1:0] = ‘01’ tdat[31:8] is valid.

When tmod[1:0] = ‘10’ tdat[31:16] is valid.

When tmod[1:0] = ‘11’ tdat[31:24] is valid.

When tmod[1:0] should only be asserted when teop is asserted.