Timing –29, Timing – Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 57

Chapter 3: Functional Description

3–29

Interface Signals

© November 2009

Altera Corporation

POS-PHY Level 2 and 3 Compiler User Guide

Preliminary

Timing

For a slave source to master sink there is a single-cycle delay after ena is asserted or

deasserted and dataflow on dat (and associated data interface signals) starts or stops.

However, the interface is pipelined, so the delay does not affect the net throughput of

the interface.

Figure 3–18 on page 3–30

shows the timing of the Atlantic interface with a master

sink.

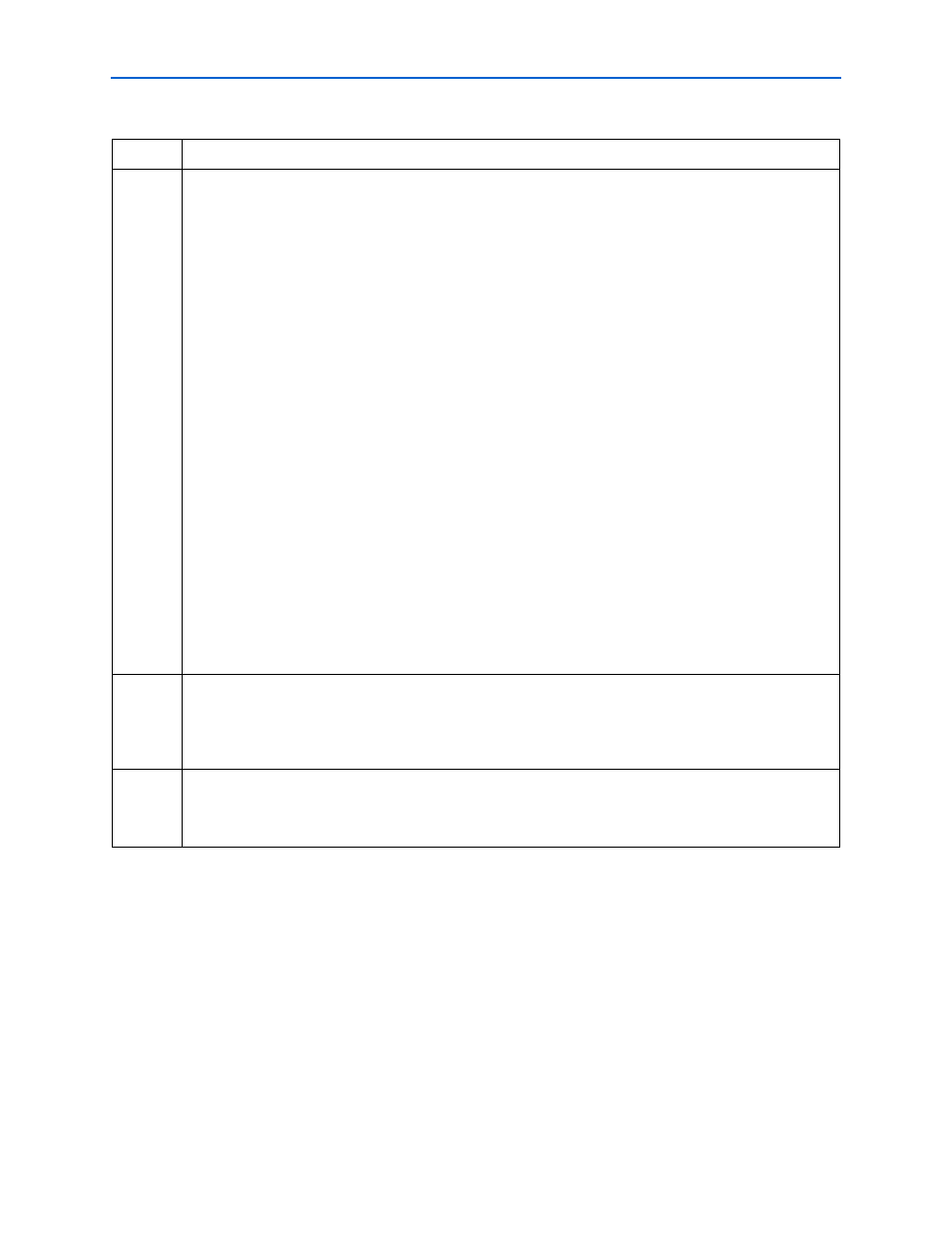

Table 3–14. Atlantic Interface Control Signals

Signal

Description

ena

Data transfer enable. ena is always driven by the master and controls the data flow across the interface.

When the master is the source, ena behaves as a write enable from master to slave. The master asserts ena

and dat simultaneously. When the slave observes ena asserted on the clk rising edge, it immediately

captures the Atlantic data interface signals (see

Figure 3–20

).

When the slave is the source, ena behaves as a read enable from master to slave. When the slave observes

ena

asserted on the clk rising edge it drives, on the next clk edge, the Atlantic data interface signals and

asserts val. The master captures the data interface signals on the following clk rising edge. If the slave is

unable to provide new data, it deasserts val for one or more clock cycles until it is prepared to drive valid data

interface signals.

For POS-PHY level 2 and 3 source variations that uses an Atlantic master sink interface on the B-side, the

bN_ena

output signals on the Atlantic master sink interfaces are not guaranteed to be zero during reset

(bN_reset_n low). Instead, these signals reflect the value of the bN_dav input signals.

The bN_ena signal may be asserted despite the assertion of the bN_reset_n signal. If your Atlantic source

slave logic asserts the bN_dav while the POS-PHY Level 2 and 3 MegaCore function is in reset, the MegaCore

function inadvertently begins to read data from the sink logic. The data read is not stored in the MegaCore

function’s buffers nor is it transmitted, which results in lost data.

Ensure that the bN_dav input to the MegaCore function holds the desired value for bN_ena while the

MegaCore function is in reset, which can be implemented in one of the following ways:

■

Ensure that the Atlantic slave source logic is reset while the MegaCore function is in reset.

■

Drive the bN_dav input signal from a flip-flop reset by bN_reset_n and fed by your desired dav signal.

val

Data valid. Present only on a slave source and master sink interface. When high, val indicates valid data

signals. val is updated on every clock edge where ena is sampled asserted, and holds its current value along

with the dat bus where ena is sampled deasserted. Invalid signals (val low) must be disregarded. To

determine whether new data has been received, the master must qualify the val signal with the previous state

of the ena signal.

dav

Data available. When the dat bus is in slave to master direction, if dav is high, the slave has at least

threshold

words available to be read, or the data can be read up to an end of packet without risk of

underflow. When the dat bus is in master to slave direction, if dav is high, the slave has enough space for

threshold

words to be written.

(1)

Note to

Table 3–13

:

(1) threshold is implementation dependent and typically corresponds to FIFO buffer almost full/empty levels.