Performance and resource utilization, Performance and resource utilization –5 – Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 9

Chapter 1: About This Compiler

1–5

Performance and Resource Utilization

© November 2009

Altera Corporation

POS-PHY Level 2 and 3 Compiler User Guide

Preliminary

You only need to purchase a license for the megafunction when you are completely

satisfied with its functionality and performance, and want to take your design to

production.

f

For more information on OpenCore Plus hardware evaluation using the POS-PHY

Level 2 and 3 Compiler, see

“OpenCore Plus Time-Out Behavior” on page 3–6

Performance and Resource Utilization

Table 1–3

through

1–7

show typical expected performance for SPHY and 4-port POS-

PHY MegaCore functions. All results are push-button performance and use a FIFO

buffer size of 512 bytes. These results were obtained using the Quartus

®

II software

version for the following devices:

■

Cyclone II (see tables for device details)

■

Cyclone III (EP3C5F256C6 for POS-PHY level 3)

■

Stratix III (EP3SL70F484C2 for POS-PHY level 2; EP3SL50F484C2 for POS-PHY

level 3)

■

Stratix IV (EP4SGX70DF29C2X )

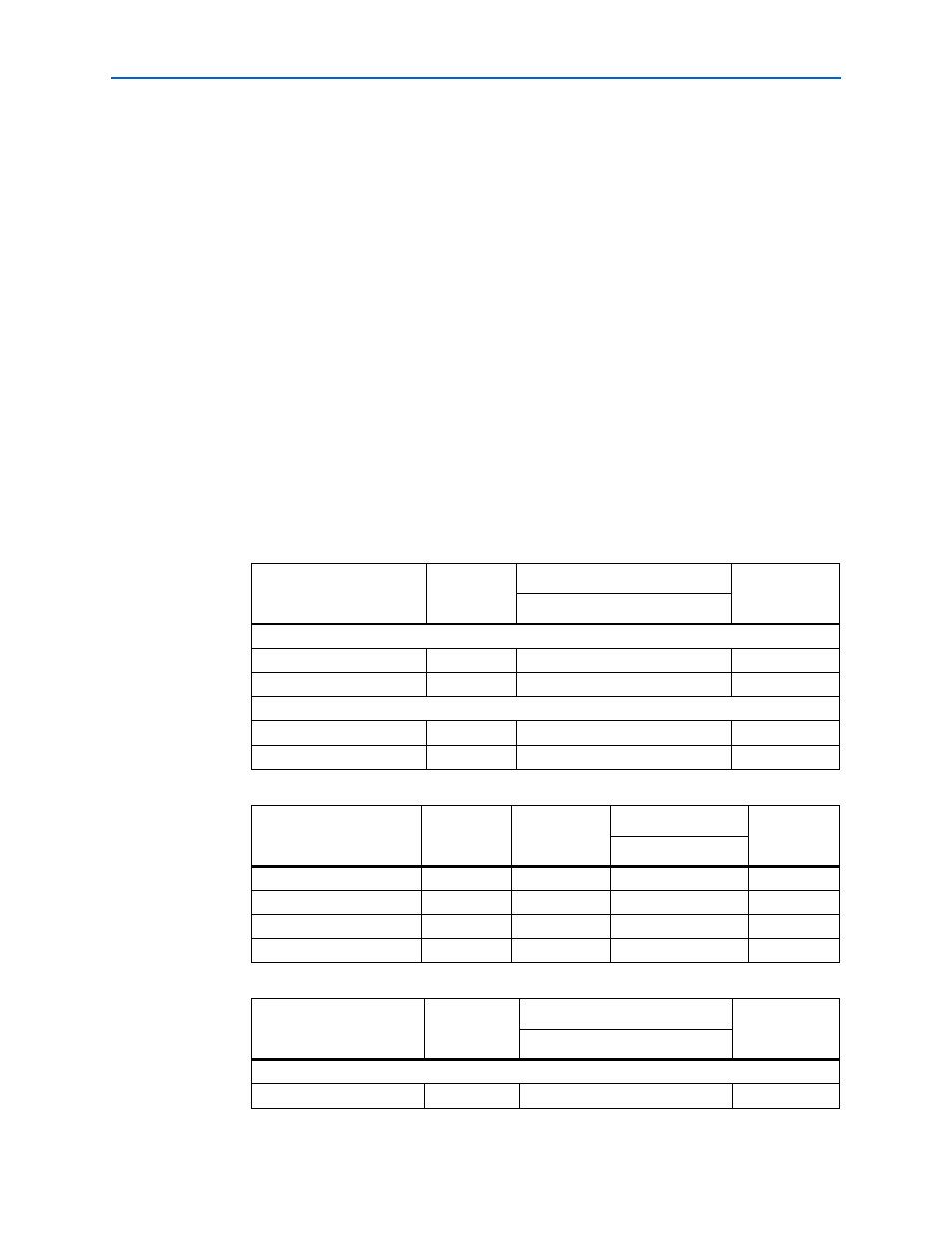

Table 1–3. Performance—POS-PHY Level 2 Link Layer—Cyclone II Device

MegaCore Function

LEs

Memory Blocks

f

MAX

(MHz)

M4K

Device: EP2C5F256C6

SPHY receive

416

2

176

SPHY transmit

407

2

149

Device: EP2C15AF484C6

MPHY 4-port receive

1,267

8

167

MPHY 4-port transmit

1,272

8

128

Table 1–4. Performance—POS-PHY Level 2 Link Layer—Stratix III Device

MegaCore Function

ALUTs

Logic

Registers

Memory Blocks

f

MAX

(MHz)

M9K

SPHY receive

177

348

2

344

SPHY transmit

210

326

2

310

MPHY 4-port receive

558

1,051

8

320

MPHY 4-port transmit

624

1,024

8

221

Table 1–5. Performance—POS-PHY Level 2 PHY Layer—Cyclone II Device (Part 1 of 2)

MegaCore Function

LEs

Memory Blocks

f

MAX

(MHz)

M4K

Device: EP2C5F256C6

SPHY receive

354

2

174