Megacore verification, Compatibility –31 example packet types –31, Megacore verification –31 – Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 59: Compatibility, Example packet types

Chapter 3: Functional Description

3–31

MegaCore Verification

© November 2009

Altera Corporation

POS-PHY Level 2 and 3 Compiler User Guide

Preliminary

Compatibility

To ensure that individual implementations of an Atlantic interface are compatible

they must have the following:

■

The same data bus width

■

Compatible data directions (data source connecting to data sink)

■

Compatible control interfaces (master interface connecting to slave interface)

■

Compatible FIFO buffer threshold levels (slave sink can overflow, and slave

source can operate inefficiently if thresholds are incorrectly set)

Example Packet Types

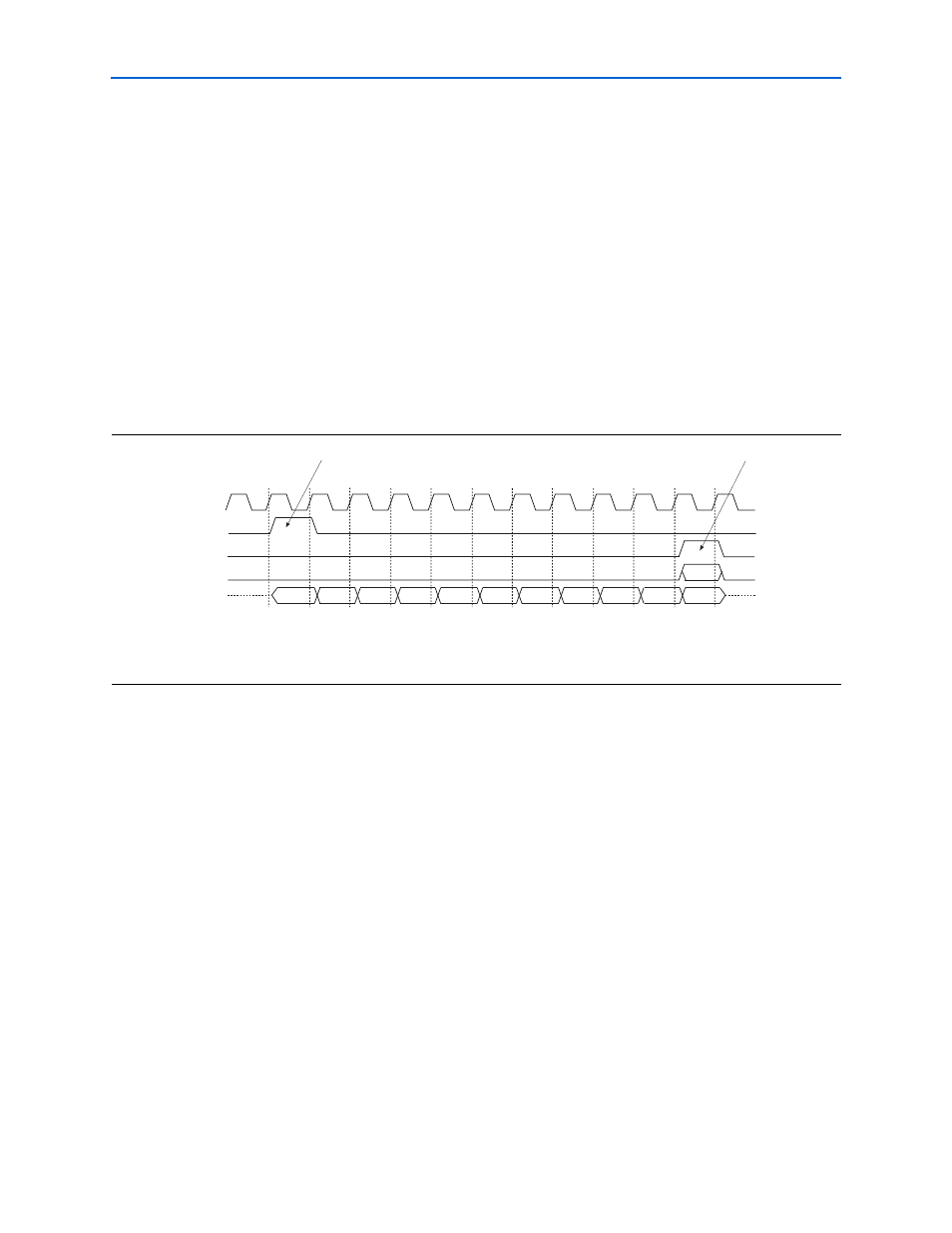

Figure 3–20

shows an example data packet. The assumption is that ena and val are

continuously asserted.

MegaCore Verification

Before releasing a version of the POS-PHY Level 2 and 3 Compiler, Altera runs a

comprehensive regression test, which executes the wizard to create the instance files.

Next, VHDL testbenches are run in the ModelSim simulator, to exercise the VHDL

models. The regression suite covers various parameters such as input and output

interface types and bus widths, varying FIFO buffer parameters, and relevant

architecture options.

Several computers automatically run these simulations for many days, to ensure that

the MegaCore function is robust. In addition to automated computerized regression

testing, human testers use IP Toolbench and test many combinations of options and

buttons.

The POS-PHY Level 2 and 3 Compiler has also been verified for interworking with

simulation models for two PMC-Sierra chips. The PM5351 uses a POS-PHY level 2, 4-

channel, PHY interface and was tested by connecting a POS-PHY level 2 link interface

(configured by the POS-PHY Level 2 and 3 Compiler). The PM7325 uses a POS-PHY

level 3 PHY-layer or link-layer interface, and was tested by connecting a POS-PHY

level 3 link-layer or PHY-layer interface (configured by the POS-PHY Level 2 and 3

Compiler). In all cases packets of random length were successfully passed through the

system, and verified at the other end.

Figure 3–20. Example Data Packet

Notes to

Figure 3–20

:

(1) sop marks the start of the data packet.

(2) eop marks the end of the data packet, and mty indicates the number of invalid bytes.

clk

sop

eop

mty

dat

(1)

(2)