Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 48

3–20

Chapter 3: Functional Description

Interface Signals

POS-PHY Level 2 and 3 Compiler User Guide

© November 2009

Altera Corporation

Preliminary

1

These signals are compliant with the POS-PHY Level 3 Specification, Issue 4, June

2000.

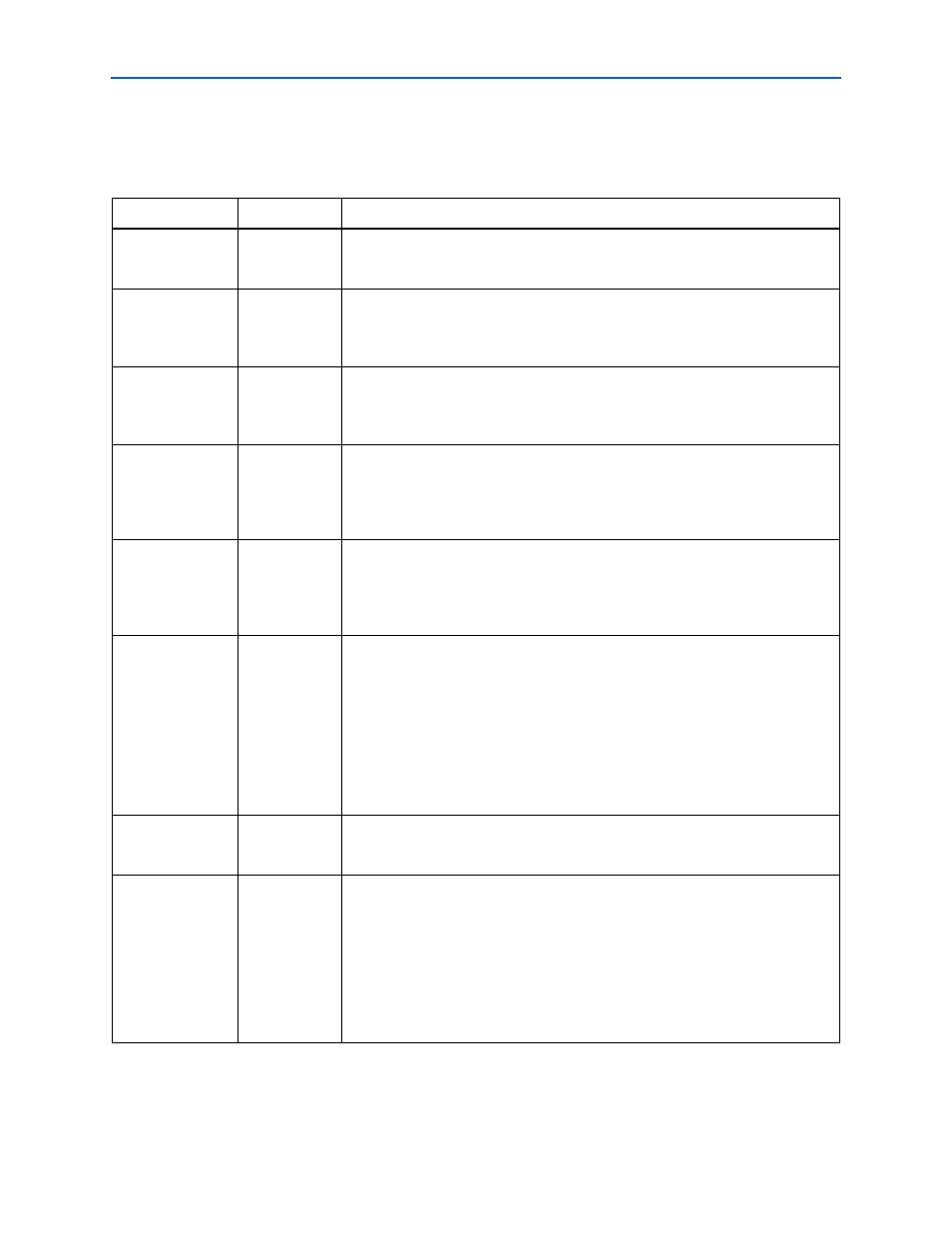

Table 3–10. POS-PHY Level 3 Receive Interface (Part 1 of 2)

Signal

Direction

Description

rfclk

Input

Receive FIFO buffer write clock. rfclk is used to synchronize data-transfer

transactions between the link-layer device and the PHY-layer device. rfclk can

cycle at a rate up to 104 MHz.

rdat[31/7:0]

PHY to link

Receive packet data bus. The rdat bus carries the packet octets that are read from

the receive FIFO buffer. rdat is valid only when rval is asserted. Data must be

received in big-endian order on rdat. When an 8-bit interface is used, only

rdat[7:0]

is supported.

rsop

PHY to link

Receive start of packet. rsop delineates the packet boundaries on the rdat bus.

When rsop is high, the start of the packet is present on the rdat bus. rsop must

be present at the beginning of every packet and is valid only when rval is

asserted.

reop

PHY to link

Receive end of packet. reop delineates the packet boundaries on the rdat bus.

When reop is high, the end of the packet is present on the rdat bus. rmod

indicates the number of valid bytes the last double-word is composed of, when

reop

is asserted. reop is required to be present at the end of every packet and is

valid only when rval is asserted.

rerr

PHY to link

Receive error indicator. rerr is used to indicate that the current packet is aborted

and should be discarded. rerr should only be asserted when reop is asserted.

Conditions that can cause rerr to be set can be, but are not limited to, FIFO buffer

overflow, abort-sequence detection, missing SOP, missing EOP, and parity errors.

terr

is asserted at its input. rerr is valid only when rval is asserted.

rmod[1:0]

PHY to link

Receive word modulo signal. rmod indicates the number of valid bytes of data in

rdat

. The rmod bus should always be all zero, except during the last double-word

transfer of a packet on rdat. When reop is asserted, the number of valid packet

data bytes on rdat is specified by rmod

When rmod[1:0] = ‘00’ rdat[31:0] is valid.

When rmod[1:0] = ‘01’ rdat[31:8] is valid.

When rmod[1:0] = ‘10’ rdat[31:16] is valid.

When rmod[1:0] = ‘11’ rdat[31:24] is valid

rmod

is valid only when rval is asserted.

rprty

PHY to link

Receive parity signal. rprty indicates the parity calculated over the rdat bus.

When rprty is supported, the PHY-layer device must support both odd and even

parity.

renb

Link to PHY

Receive read enable (see

Figure 3–16

). renb controls the flow of data from the

receive FIFO buffers. During data transfer, rval must be monitored, as it indicates

if rdat, rprty, rmod, rsop, reop, rsx, and rerr are valid. The system can

deassert renb at anytime, if it is unable to accept data from the PHY device. When

renb

is sampled low by the PHY device, a read is performed from the receive FIFO

buffer. rdat, rprty, rmod, rsop, reop, rerr, rsx, and rval are updated

on the following rising edge of rfclk. When renb is sampled low by the PHY

device, a read is not performed and rdat, rprty, rmod, rsop, reop, rerr,

rsx

, and rval are not updated on the following rising edge of rfclk.