Atlantic interface, Atlantic interface –26 – Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 54

3–26

Chapter 3: Functional Description

Interface Signals

POS-PHY Level 2 and 3 Compiler User Guide

© November 2009

Altera Corporation

Preliminary

Atlantic Interface

The Atlantic interface is a full-duplex synchronous point-to-point connection

protocol. The POS-PHY Level 2 and 3 Compiler supports data widths of 8, 16, 32, and

64 bits on the Atlantic interface.

f

For further information on the Atlantic interface, refer to the Atlantic Interface

Functional Specification.

Figure 3–17

shows the following two Atlantic interface control options (and all four

interface types):

■

Master source to slave sink

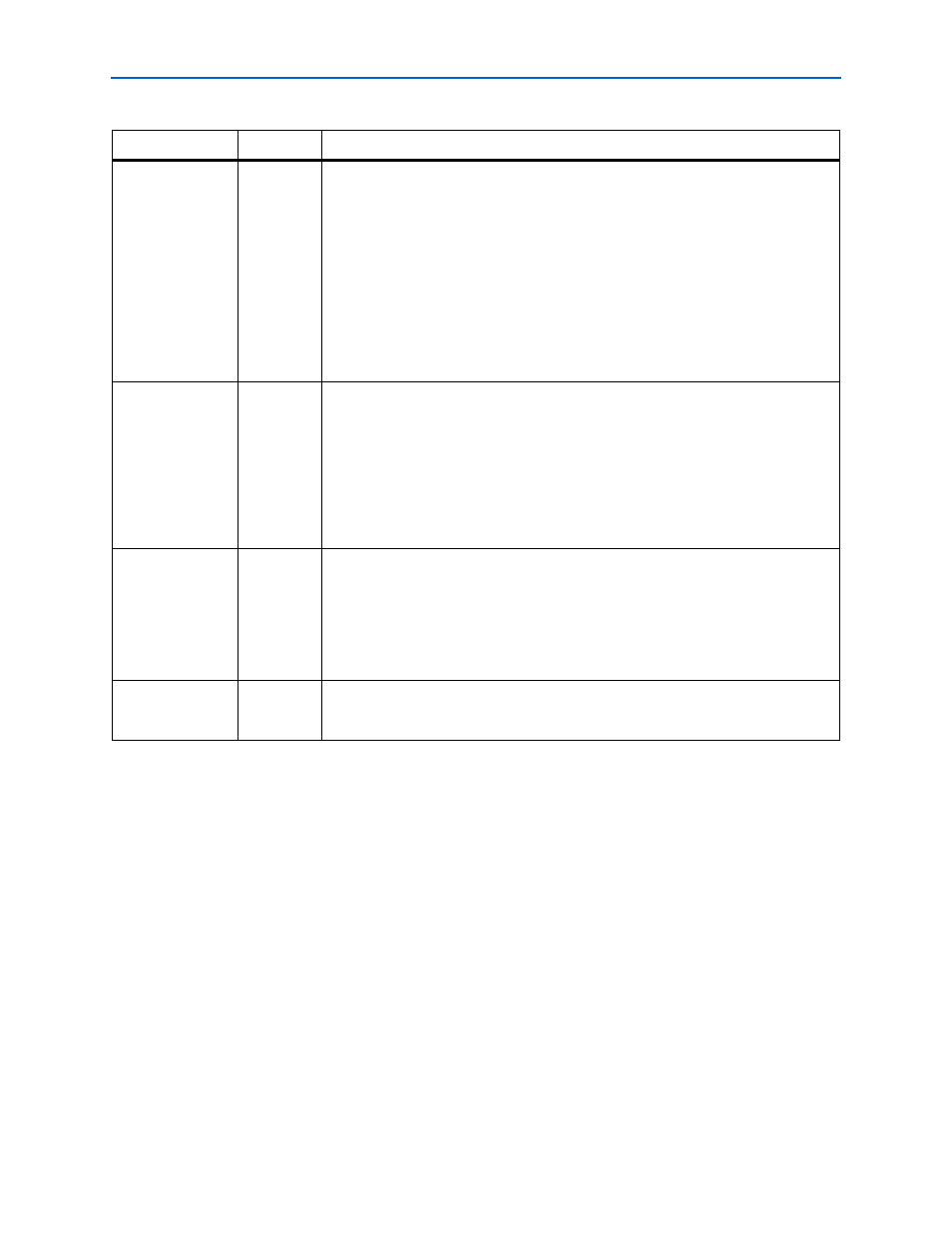

rval

PHY to link

Receive data valid signal. rval indicates the validity of the receive data signals. When

rval

is high, the receive signals (rdat, rsop, reop, rmod, rxprty and rerr)

are valid. When rval is low, all receive signals are invalid and must be disregarded.

rval

transitions low on a FIFO buffer empty condition or on an end of packet. Data is

not removed from the receive FIFO buffer while rval is deasserted. When deasserted,

rval

remains deasserted until current the PHY has been deselected. rval allows you

to monitor the selected PHY during a data transfer, while monitoring or polling other

PHYs is done using prpa or drpa[x]. The PHY-layer device tri-states rval when

renb

is deasserted. rval is also tri-stated when either the null-PHY address (1Fh),

or an address not matching the PHY-layer device address, is presented on the radr

signals when renb is sampled high (has been deasserted during the previous clock

cycle).

prpa

(3)

PHY to link

Receive polled multi-PHY packet available signal. prpa indicates when data is available

in the polled receive FIFO buffer. When prpa is high, the receive FIFO buffer has at

least one end of packet or a predefined number of bytes to be read (the number of bytes

might be user programmable). prpa is low when the receive FIFO buffer fill level is

below the assertion threshold and the FIFO buffer contains no end of packet. prpa

allows to poll every PHY while transferring data from the selected PHY. prpa is driven

by a PHY-layer device when its address is polled on radr. A PHY-layer device tri-

states prpa when either the null-PHY address (1Fh), or an address not matching

available PHY-layer devices, is provided on radr.

drpa[x]

(4)

PHY to link

Receive packet available direct status indication signals. These signals provides direct

status indication for the corresponding port (referred to by “x”). drpa[x] indicates

when data is available in the receive FIFO buffer. When drpa[x] is high, the receive

FIFO buffer has at least one end of packet or a predefined number of bytes to be read.

The number of bytes is user programmable. drpa[x] is low when the receive FIFO

buffer fill level is below the assertion threshold and the FIFO buffer contains no end of

packet.

rfclk

Link to PHY

Receive FIFO buffer write clock. rfclk is used to synchronize data transfer

transactions from the link-layer device to the PHY-layer device. rfclk can cycle at a

any rate from 25 MHz up to 50 MHz.

Notes to

Table 3–12

:

(1) The 8-bit mode is an Altera extension to the POS-PHY Level 2 specification.

(2) Not present in 8-bit mode.

(3) Packet-level mode only.

(4) Byte-level mode only.

Table 3–12. POS-PHY Level 2 Receive Interface (Part 3 of 3)

Signal

Direction

Description