Parity settings, Common b clock –8, Parity settings –8 – Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 36: Pass through mode –8

3–8

Chapter 3: Functional Description

Parameters

POS-PHY Level 2 and 3 Compiler User Guide

© November 2009

Altera Corporation

Preliminary

■

B Clock—the corresponding ‘B’ interface uses an internal dual clock FIFO buffer,

and is clocked by the corresponding ‘B’ interface clock pin

The FIFO buffer width is the greater of the A bus width and the associated B bus

width.

Common B Clock

With MPHY configurations there is more than one ‘B’ interface in the MegaCore

function. Select this option to use a common clock and reset pins for all the ‘B’

interfaces that use the B clock option.

If you select this option, the ‘B’ interface clock and reset pins are labeled b_clk and

b_reset_n

.

Parity Settings

This section describes pass through mode and the parerr on error pin.

Pass Through Mode

In pass through mode any detected data parity errors on a sink interface are

regenerated on the source interface, even when there is a bus width change.

1

If a parity error is detected on a sink interface port that has a wider data width than its

corresponding source interface port, the parity error is generated on all output words

that correspond to the input word with an error.

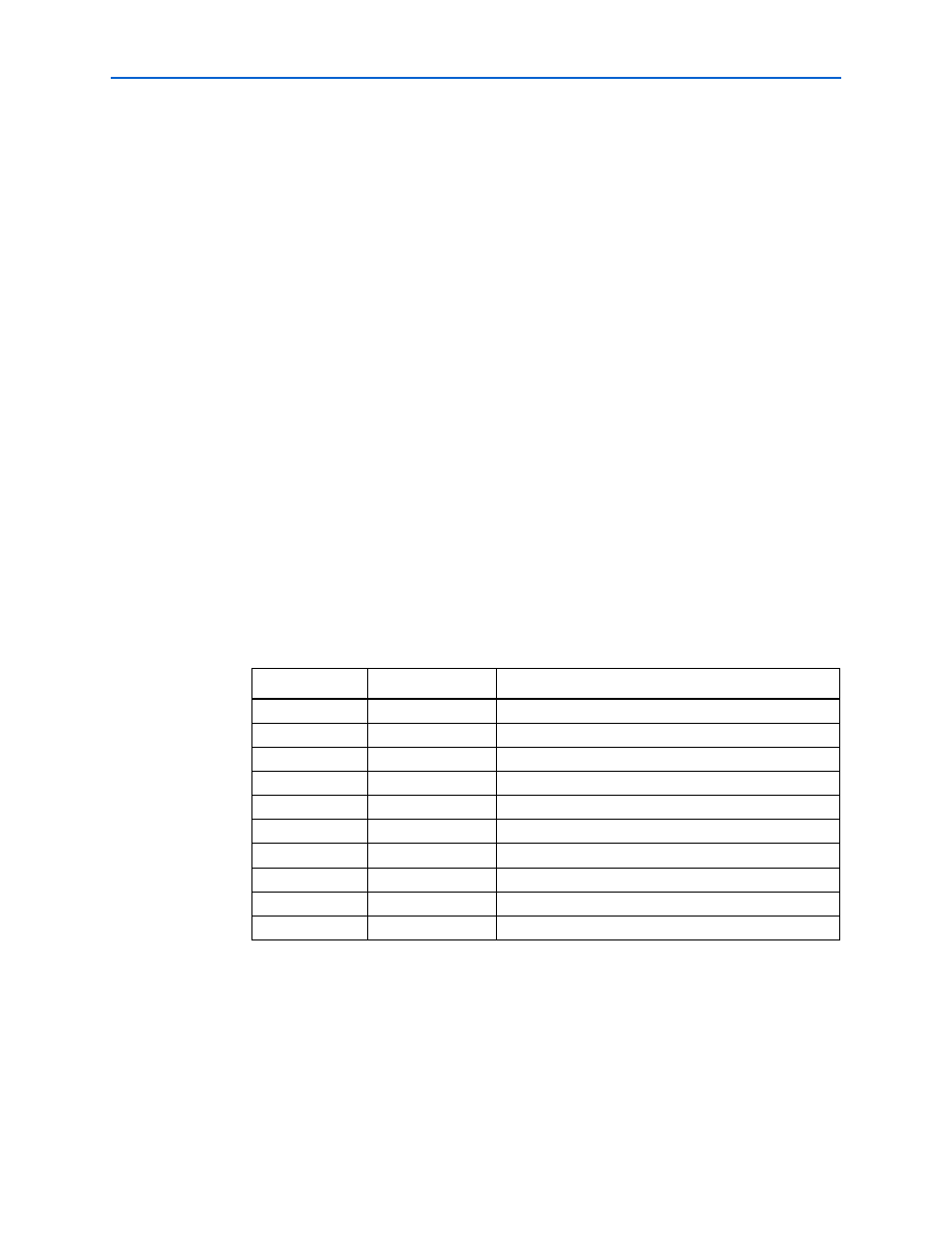

Table 3–2

shows the number of errors generated per input error.

If you are using the parity bit and the parity does not match the data, the MegaCore

function always detects the parity error.

For a source Atlantic interface, the par pin is an output that indicates the sink

interface has received parity errors.

For a sink Atlantic interface, the par pin is an input that sees either a one or a zero

depending on the incoming data’s parity value.

Table 3–2. Number of Errors Generated

Data Width In

Data Width Out

Number of Errors Generated per Input Error

64

8

8

64

16

4

64

32

2

64

64

1

32

8

4

32

16

2

32

32

1

16

8

2

16

16

1

8

8

1