Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 51

Chapter 3: Functional Description

3–23

Interface Signals

© November 2009

Altera Corporation

POS-PHY Level 2 and 3 Compiler User Guide

Preliminary

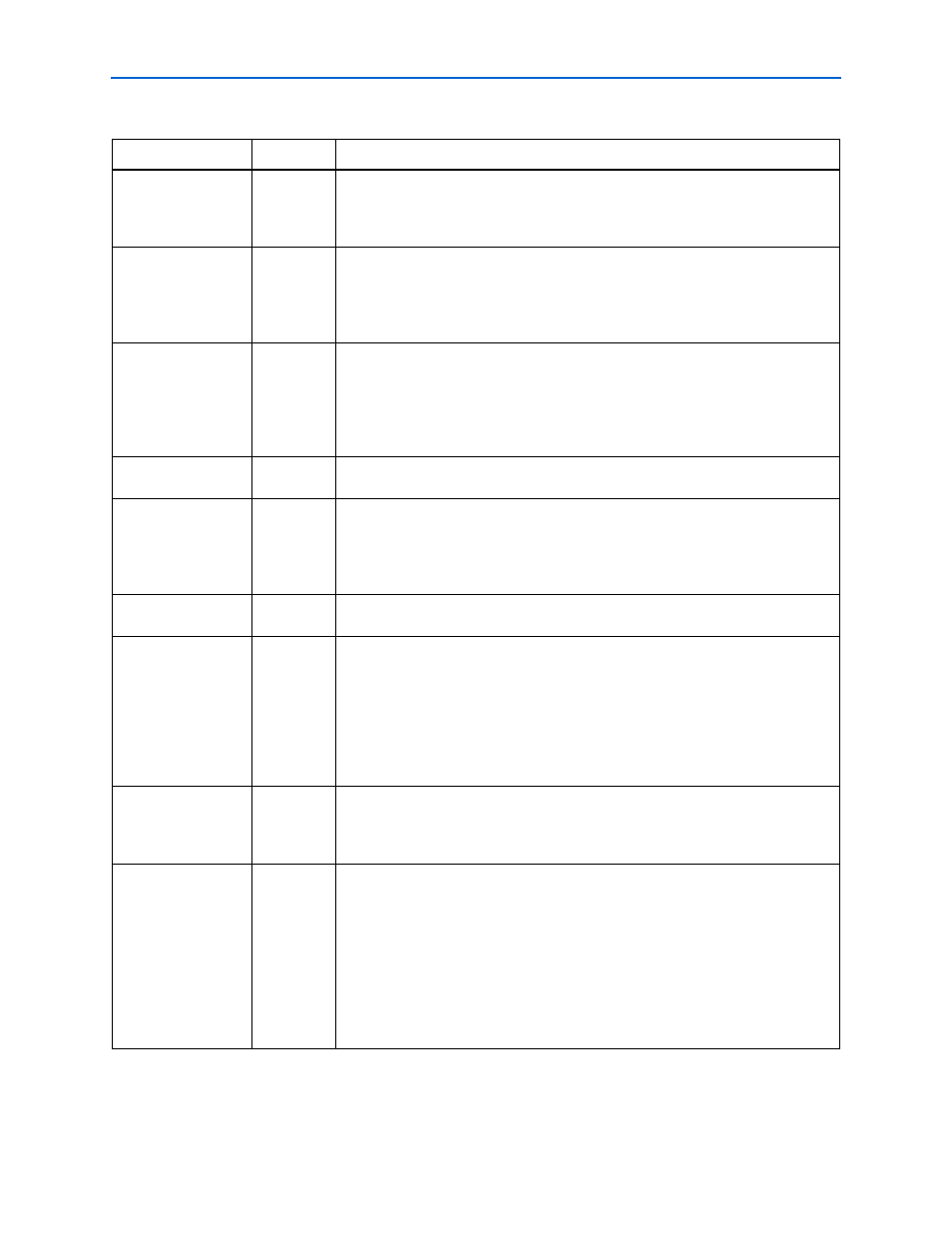

Table 3–11. POS-PHY Level 2 Transmit Interface (Part 1 of 2)

Signal

Direction

Description

tdat[15/7:0]

(1)

Link to PHY

Transmit packet data bus. tdat carries the packet octets that are written to the

selected transmit FIFO buffer. tdat is valid only when tenb is simultaneously

asserted. Data must be transmitted in big-endian order. Given the previously defined

data structure, bits are transmitted in the following order: 15, 14 … 8, 7, 6 … 1, 0.

tprty

Link to PHY

Transmit bus parity. tprty indicates the parity calculated over the whole tdat

bus. When tprty is supported, the PHY-layer device is required to support both

even and odd parity. The PHY-layer device reports any parity error to higher layers

but does not interfere with the transferred data. tprty is valid only when tenb is

asserted.

tmod

(2)

Link to PHY

The transmit word modulo. tmod indicates the size of the current word. tmod

should always be low, except during the last word transfer of a packet (when teop

is asserted). During a packet transfer every word must be complete except the last

word, which can comprise 1 or 2 bytes. When set high, tmod indicates a 1-byte

word (present on MSBs, LSBs are discarded); when set low, tmod indicates a 2-byte

word.

tsop

Link to PHY

Transmit start of packet. tsop indicates the first word of a packet. tsop must be

present at the beginning of every packet and is valid only when tenb is asserted.

teop

Link to PHY

Active-high transmit end of packet. teop marks the end of a packet on the tdat

bus. When teop is high, the last word of the packet is present on the tdat stream

and tmod indicates how many bytes this last word is composed of. tsop must not

be high when teop is high. teop provides support for one or two bytes packets, as

indicated by the value of tmod.

terr

Link to PHY

The transmit error indicator. terr must only be asserted during the last word

transfer of a packet.

tenb

Link to PHY

Transmit MPHY write enable. tenb is an active low input and is used along with the

tadr

inputs to initiate writes to the transmit FIFO buffers. POS-PHY supports byte-

level and packet-level transfer. Packet-level transfer operates with a selection phase

when tenb is deasserted and a transfer phase when tenb is asserted. While tenb

is asserted, tadr is used for polling ptpa. Byte-level transfer works on a cycle

basis. When tenb is asserted data is transferred to the selected PHY. Nothing

happens when tenb is deasserted. Polling is not available in byte-level transfer

mode, and direct packet availability is provided by dtpa[x].

tadr[4:0]

Link to PHY

Transmit PHY address bus. The tadr bus is used to select the FIFO buffer (and

hence the port) that is written to using the tenb signal, and the FIFO buffer whose

packet-available signal is visible on the PTPA output when polling. Address 1Fh is

the null-PHY address and must not be identified to any port on the POS-PHY bus.

stpa

(3)

PHY to link

Selected-PHY transmit packet available signal. stpa transitions high when

fifo_threshold

words are available in the selected transmit FIFO buffer (the

one data is written into). When high, stpa indicates that the transmit FIFO buffer is

not full. When stpa transitions low, it indicates that the transmit FIFO buffer has

reached fifo_threshold words. stpa always provides status indication for the

selected PHY to avoid FIFO buffer overflows while polling is performed. The PHY-

layer device tri-states stpa when tenb is deasserted. stpa is also tri-stated when

either the null-PHY address (1Fh), or an address not matching the PHY-layer device

address, is presented on the tadr signals when tenb is sampled high (has been

deasserted during the previous clock cycle).