Features, Features –2 – Altera POS-PHY Level 2 and 3 Compiler User Manual

Page 6

1–2

Chapter 1: About This Compiler

Features

POS-PHY Level 2 and 3 Compiler User Guide

© November 2009

Altera Corporation

Preliminary

Features

■

Conforms to POS-PHY level 2 and level 3 specifications

■

Link-layer or PHY-layer POS-PHY interfaces

■

Creates bridges between different POS-PHY interfaces

■

Support for traffic up to a rate of 3.2 gigabits per second (Gbps) (POS-PHY level 3)

or 832 megabits per second (Mbps) (POS-PHY level 2), such as SONET OC-48

■

Single-PHY (SPHY) or up to 8-channel multi-PHY (MPHY) operation with polled

and direct packet available options

■

Atlantic

™

interface that allows a consistent interface between all Altera cell and

packet MegaCore functions

■

Selectable POS-PHY interface bus widths (8/16/32 bit) and Atlantic interface bus

widths (8/16/32/64 bit)—allowing translation between different bus types

■

Parity generation/detection

■

Configurable first-in first-out (FIFO) options: selectable FIFO width, depth, and fill

thresholds.

■

Easy-to-use IP Toolbench interface

■

IP functional simulation models for use in Altera-supported VHDL and Verilog

HDL simulators

■

Support for OpenCore Plus evaluation

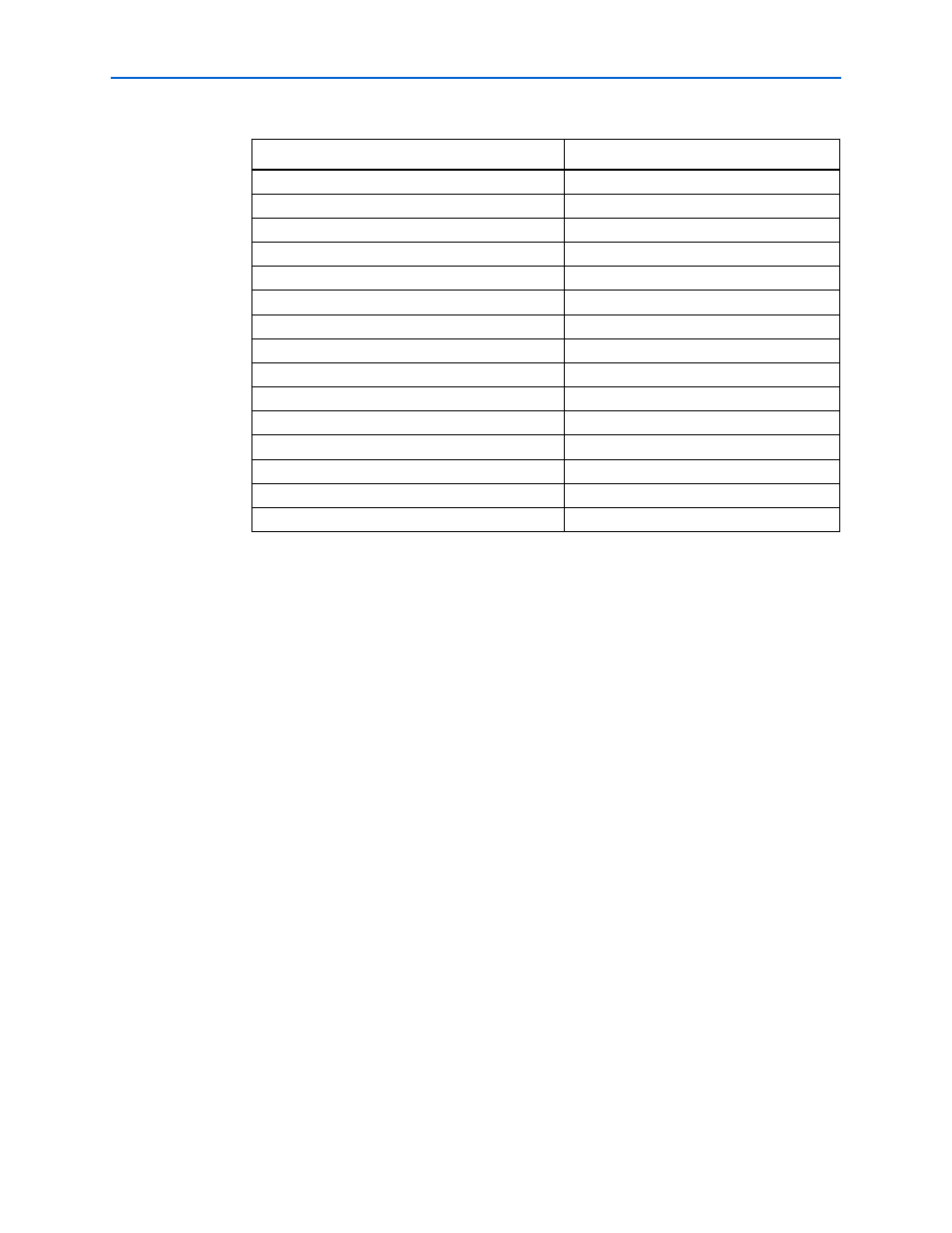

Table 1–2. Device Family Support

Device Family

Support

Arria

™

GX

Full

Arria II GX

Preliminary

Cyclone

®

Full

Cyclone II

Full

Cyclone III

Full

HardCopy

®

II

Full

HardCopy III

Preliminary

HardCopy IV E

Preliminary

Stratix

®

Full

Stratix II

Full

Stratix II GX

Full

Stratix III

Full

Stratix IV

Preliminary

Stratix GX

Full

Other device families

No support