9 synchronization, 1 supported sync modes, Synchronization – BECKHOFF ET9300 User Manual

Page 57: Supported sync modes

Application Note ET9300

55

9

Synchronization

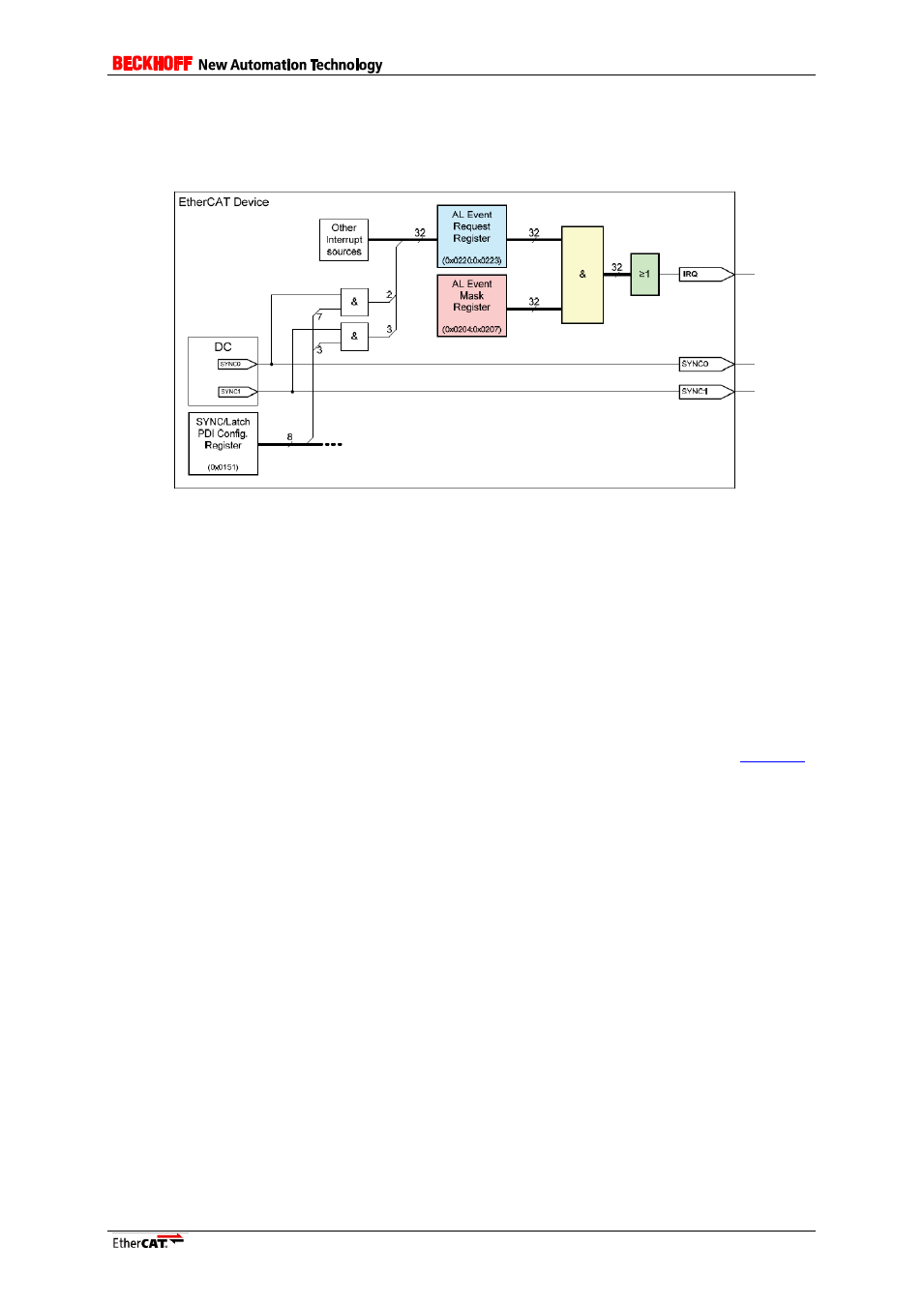

The Slave Stack Code supports different modes of synchronisation which are based on three physical

signals: (PDI_)IRQ, Sync0 and Sync1 (Figure 15: ESC Interrupt Signals).

Figure 15: ESC Interrupt Signals

Which of these signals are supported by the stack are based on the following settings.

AL_EVENT_ENABLED: Enable/Disable the (PDI_)IRQ support. The interrupt can be triggered by

different event which are controlled by the AL event register (0x220:0x223) and the AL event mask

register (0x204:0x207). For further details see the ESC datasheet. By default only the process data

event (process data was written to SyncManager2 or process data was read from SyncManger3)

triggers the interrupt.

DC_SUPPORTED: Enable/Disable the handling of the Sync0/Sync1 signals generated by the DC

UNIT.

9.1

Supported Sync Modes

If AL_EVENT_ENABLED and DC_SUPPORTED are disabled, then the SSC is operating in

(slave application is not synchronized with EtherCAT cycle) mode.

Otherwise the synchronisation mode is configured by the SyncTypes 0x1C32.1 and 0x1C33.1 (see [7]

). If no CoE is supported or no SyncType is written (during the state transition from PreOP to SafeOP)

, then the synchronisation mode is set based on the DC activation register (0x981, ESI element:

“Dc/OpMode/AssignActivate”).

In Table 7 the supported Sync Modes are listed including the corresponding settings, if no SyncType

was set before (writing 0x1C32:1 and 0x1C33:1).