Fluke Biomedical 956A-201-M2 User Manual

Page 55

3-29

Data Transceivers

Data transceiver U16 is an octal tri-state bi-directional transceiver that provides drive capability to the data

bus. The MPU data I/O signals are connected to U16 "A" ports. U16 "B" ports drive the data bus under

control of the read/write signal. When U16-11 is low, data is transferred from the "B" ports (internal bus) to

the "A" ports (MPU data). When U16-11 is high, data is transferred from the "A" ports (MPU data) to the

"B" ports (internal bus) during a write cycle.

Data transceiver U73 provides buffer and drive capability to the external data bus interface, available for

optional circuit boards on J3. Data direction is controlled by the read/write line on U73-11 providing U73-9

(bus enable) is low, which enables port-to-port data transfer to occur. The bus enable signal is generated

by the option board/boards when they are addressed by the MPU. When U73-11 is low, for a read cycle,

data is transferred from the external bus to the internal bus. When U73-11 is high, for a write cycle, data is

transferred from the internal bus to the external bus.

Control Signal Buffer

Line driver U18 provides a signal drive for all system control signals and clocks utilized by circuitry within

the main circuit board.

Line driver U74 provides the drive for control lines and clock signals for external circuitry utilizing the J3

option interface connector.

Address Decoding

The master decoder (U14) is an open-collector 32 x 8 bit bipolar PROM. Address lines A15, A14, A13, and

A12 as well as /R/W are used to decode memory and I/O addresses in 4K hex blocks. Table 3-6 lists the

output signals from U14.

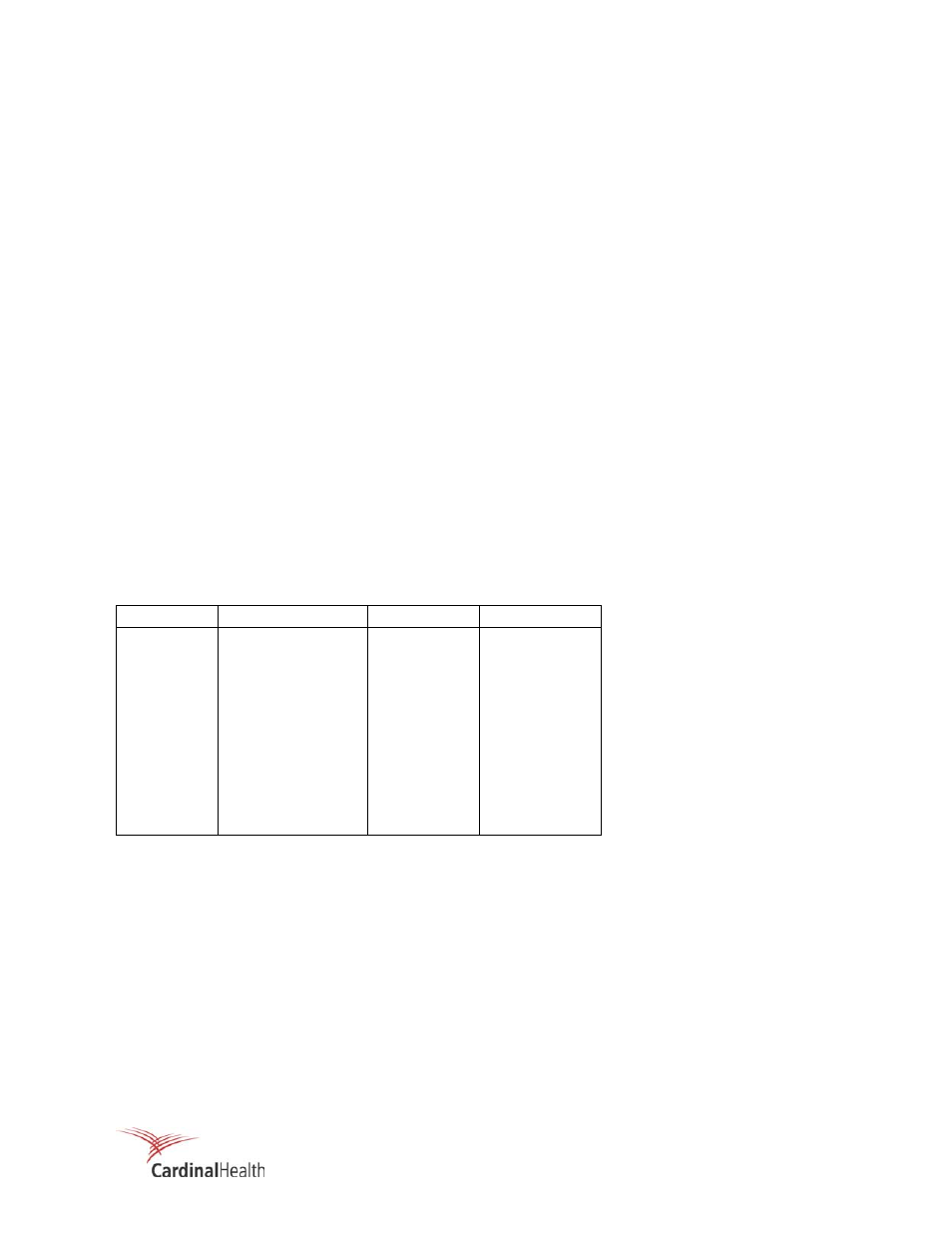

Table 3-6. Output Signal (U14)

U14 PIN

Signal Name

Address

Read/Write

9 /PROM 8000-FFFF

Read

Only

7 /SPARE Spare

6

/SPARE (RAM

2000)

2000-3FFF Read/Write

5 /RAM

0000

0000-1FFF

Read/Write

4 /IO

4000-4FFF

Read/Write

3

/RAM WRITE

0000-3FFF

Write Only

2

/RAM READ

0000-3FFF

Read Only

1 /5000 5000-5FFF

Read/Write

/PROM directly drives the enable pins of the PROM (U23). /RAM READ, /RAM 0000, and /SPARE are

logic OR'd with /CLOCK from U18 VIA logic OR circuits U17B, C, and D. /RAM READ drives the RAM

output U21 and U22 /CE (chip enable) pins. /RAM 0000 and /SPARE (RAM 2000) act as chip selects for

the appropriate RAM (U21 and U22). /RAM WRITE is logic OR’d with /WRITE 02 (from U18) by U17A,

and is connected to the write enable pins on the RAMs. The /5000 output signal is applied to line driver

U74 for connection to J3, the optional interface connector.

The /IO output signal is applied to major function decoder U1 that is a 1 of 8 decoder. U1 utilizes address

lines A5, A6, A7, and A8 as well as /CLOCK to generate outputs that are decoded in 32 hex blocks

starting at address 4000. Table 3-7 lists U1 outputs, their functions and addresses.