Altera Floating-Point User Manual

Page 148

Advertising

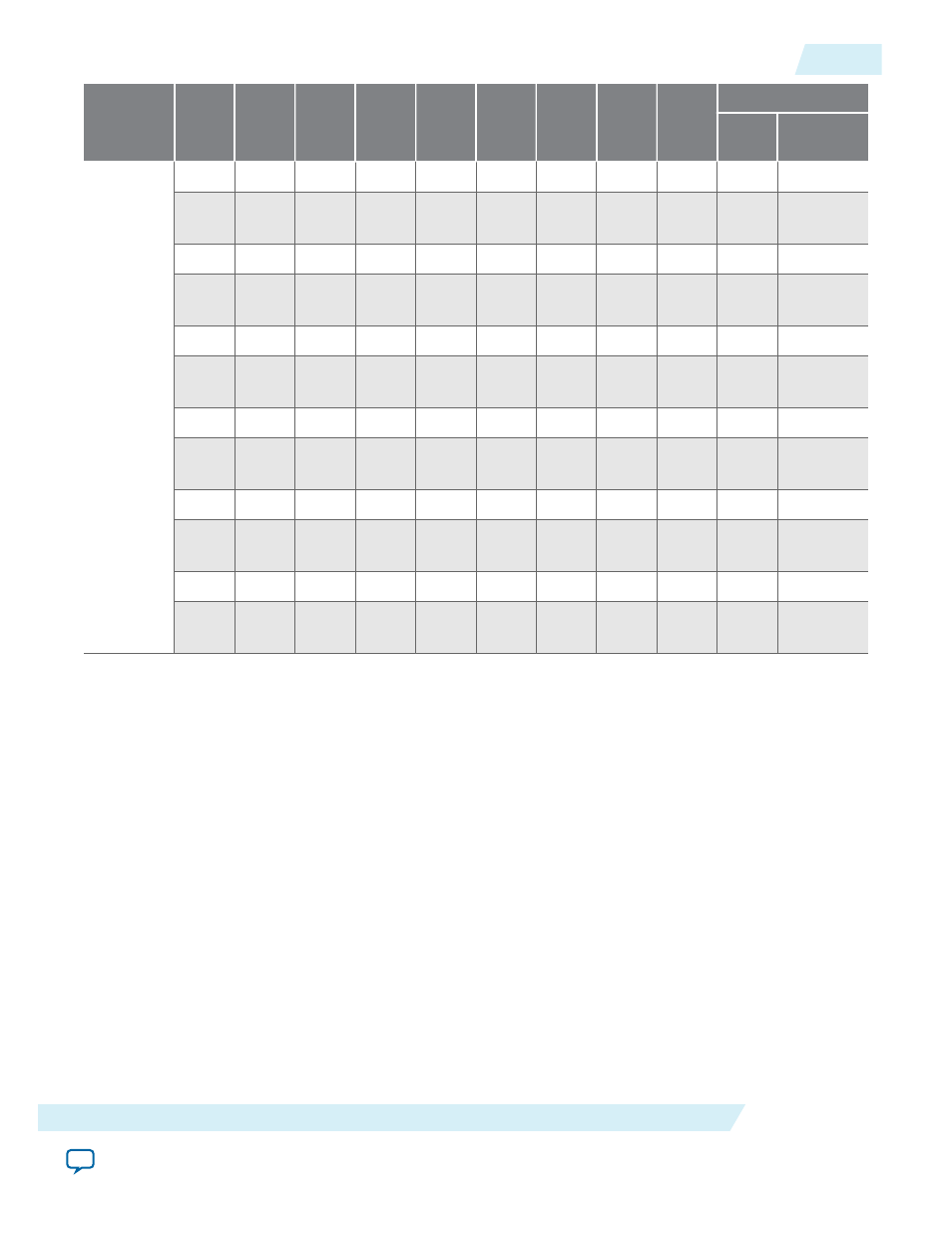

Family

Input

Width

Input

Fractio

n

Output

Precisi

on

Latenc

y

f

MAX

ALMs

M10K

M20K

DSP

Blocks

Logic Registers

Primar

y

Secondary

Cyclone

V

(5CGX

FC7D6

F31C7)

32

0

Single

8

230.04

168

0

--

0

264

21

32

0

Doubl

e

7

292.74

180

0

--

0

258

23

32

16

Single

8

230.04

168

0

--

0

264

21

32

16

Doubl

e

7

292.74

180

0

--

0

258

23

32

32

Single

8

237.14

166

0

--

0

262

20

32

32

Doubl

e

7

268.6

179

0

--

0

258

29

64

0

Single

9

248.51

219

0

--

0

391

18

64

0

Doubl

e

10

176.87

338

0

--

0

648

18

64

16

Single

9

248.51

219

0

--

0

391

18

64

16

Doubl

e

10

176.87

338

0

--

0

648

18

64

32

Single

9

248.51

219

0

--

0

391

18

64

32

Doubl

e

10

176.87

338

0

--

0

648

18

UG-01058

2014.12.19

ALTERA_FP_FUNCTIONS Resource Utilization and Performance

18-21

ALTERA_FP_FUNCTIONS IP Core

Altera Corporation

Advertising