Altera Floating-Point User Manual

Page 50

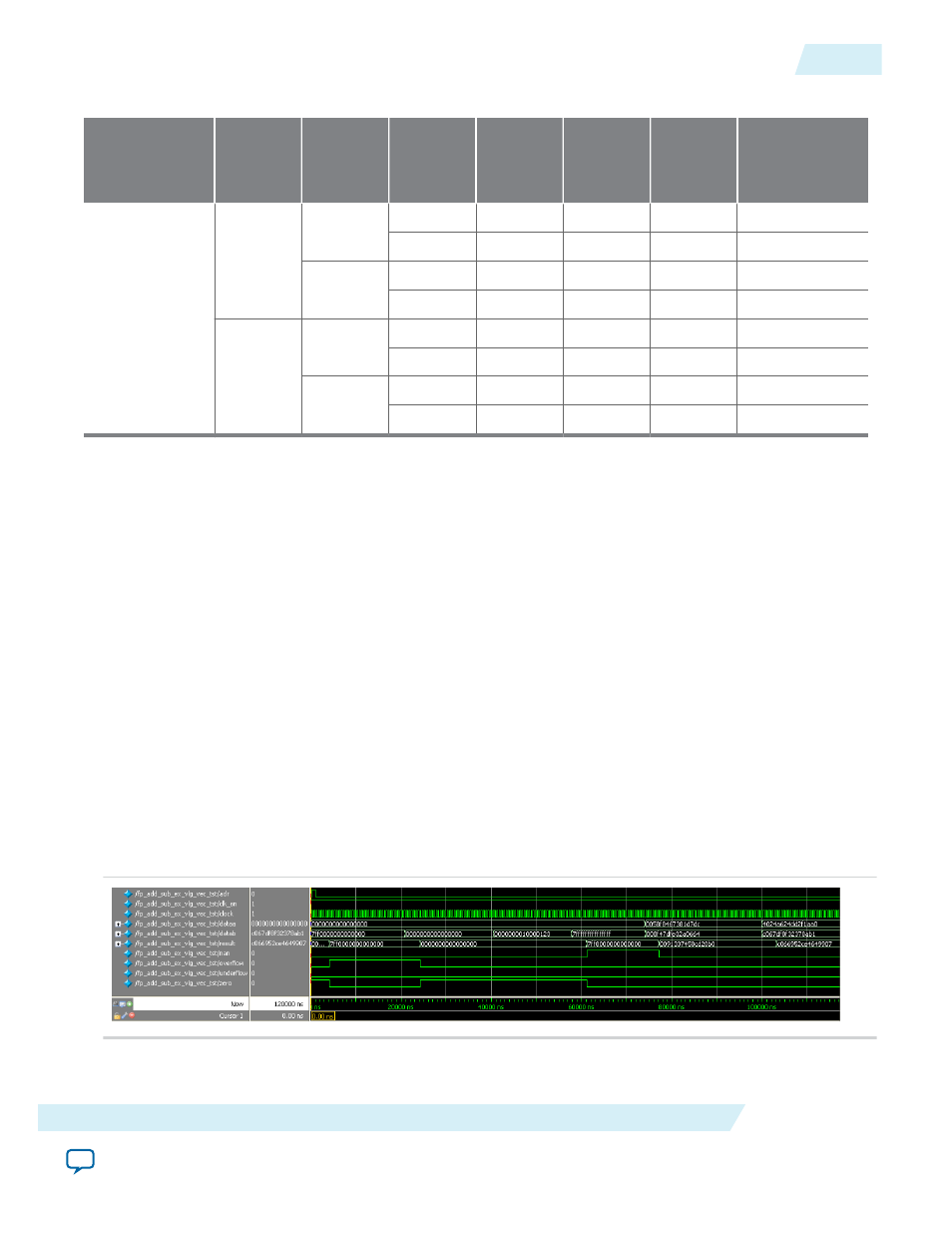

Table 5-2: ALTFP_ADD_SUB Resource Utilization and Performance for the Stratix Series of Devices

Device Family

Precision

Optimiza‐

tion

Output

latency

Adaptive

Look-Up

Tables

(ALUTs)

Dedicated

Logic

Registers

(DLRs)

Adaptive

Logic

Modules

(ALMs)

f

MAX

(MHz)

Stratix IV

single

speed

7

594

376

385

228

14

674

686

498

495

area

7

576

345

375

227

14

596

603

421

484

double

speed

7

1,198

687

824

187

14

997

1,607

1,080

398

area

7

1,106

630

762

189

14

904

1,518

1,013

265

ALTFP_ADD_SUB Design Example: Addition of Double-Precision Format

Numbers

This design example uses the ALTFP_ADD_SUB IP core to perform the addition of double-precision

format numbers using the parameter editor in the Quartus II software.

Related Information

•

Floating-Point IP Cores Design Example Files

on page 1-16

•

Provides the design example files for the Floating-Point IP cores

•

Provides information about installation, usage, and troubleshooting

ALTFP_ADD_SUM Design Example: Understanding the Simulation Results

The simulation waveform in this design example is not shown in its entirety. Run the design example files

in the ModelSim-Altera software to see the complete simulation waveforms.

Figure 5-1: ALTFP_ADD_SUB Simulation Waveform

UG-01058

2014.12.19

ALTFP_ADD_SUB Design Example: Addition of Double-Precision Format Numbers

5-3

ALTFP_ADD_SUB IP Core

Altera Corporation