Sample matrix data, Sample matrix data -8 – Altera Floating-Point User Manual

Page 32

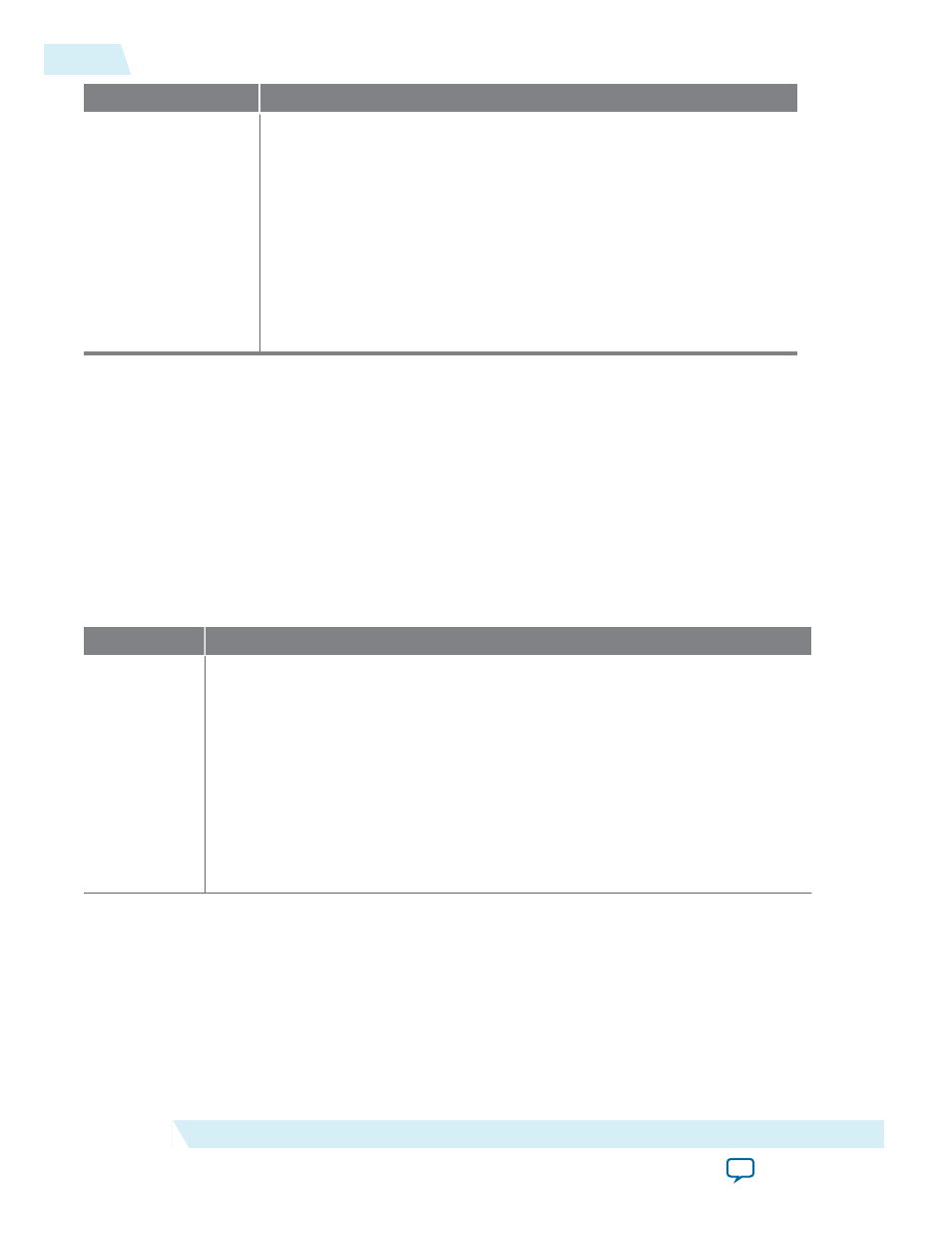

Time

Event

12527.5 –

12922.5 ns

Output stage:

• The

outvalid

signal asserts in intervals of 8 clock cycles. These series

of assertions signify the availability of valid data for the output matrix

on the

outdata[]

port.

• The output is an 8 x 8 matrix. Data is burst out regularly, row by row.

• At 12922.5 ns, the

busy

signal is asserted and the

done

signal is

deasserted.

• The assertion of the

busy

signal and the deassertion of the

done

signal

indicate that the final output is written and a new matrix can be

processed.

Sample Matrix Data

This section shows the random test data assigned to the input matrices and the results obtained from the

matrix inversion operation.

The following two sets of results are computed:

• PC-based results—these are results obtained from running the simulation in Matlab.

• FPGA-based results—these are results obtained from running the simulation in ModelSim.

This table lists the input and output data values presented in IEEE-754 Floating-point format.

Table 2-3: Input and Output Data

Matrix

Data

Input

Matrix

40c89c6c 40b16187 40e21dfb 40847306 40c00d1d 40bbf0c4 40be4fc1 40953a30

40b16187 41244acb 410e61b9 40defe3a 40f8e982 40eff916 410e0ff4 41121d78

40e21dfb 410e61b9 41217d87 40d7f5f4 40fd78fa 410618c0 41060327 40ff4517

40847306 40defe3a 40d7f5f4 40b10427 40b6be88 40bbff4a 40d12685 40ca69f9

40c00d1d 40f8e982 40fd78fa 40b6be88 41146829 40ee188a 40fa2d80 40cf065c

40bbf0c4 40eff916 410618c0 40bbff4a 40ee188a 40ecbddf 40e3aa3a 40d60773

40be4fc1 410e0ff4 41060327 40d12685 40fa2d80 40e3aa3a 4111ed09 40ecd83c

40953a30 41121d78 40ff4517 40ca69f9 40cf065c 40d60773 40ecd83c 410847da

2-8

Sample Matrix Data

UG-01058

2014.12.19

Altera Corporation

ALTERA_FP_MATRIX_INV IP Core