Altfp_div truth table, Altfp_div truth table -2 – Altera Floating-Point User Manual

Page 56

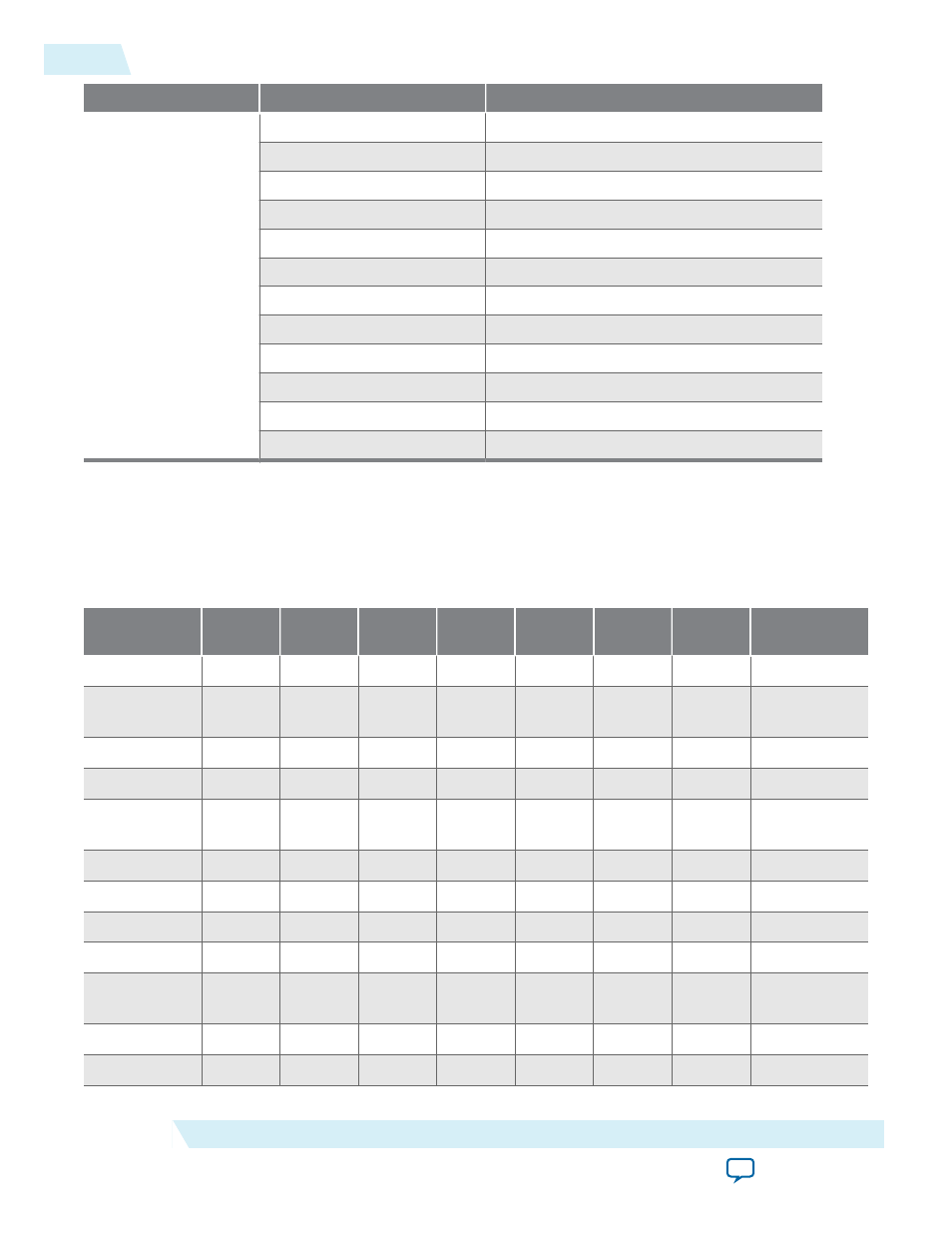

Precision

Mantissa Width

Latency (in clock cycles)

Single Extended

31 – 32

8, 18, 41

33 – 34

8, 18, 43

35 – 36

8, 18, 45

37 – 38

8, 18, 47

39 – 40

8, 18, 49

41

10, 24, 41

42

10, 24, 51

43 – 44

10, 24, 53

45 – 46

10, 24, 55

47 – 48

10, 24, 57

49 – 50

10, 24, 59

51 – 52

10, 24, 61

ALTFP_DIV Truth Table

Table 6-2: Truth Table for Division Operations

DATAA[]

DATAB[]

SIGN BIT

RESULT[] Overflow Underflo

w

Zero

Division-

by-zero

NaN

Normal

Normal

0/1

Normal

0

0

0

0

0

Normal

Normal

0/1

Denorma

l

0

0

1

0

0

Normal

Normal

0/1

Infinity

1

0

0

0

0

Normal

Normal

0/1

Zero

0

1

1

0

0

Normal

Denorma

l

0/1

Infinity

0

0

0

1

0

Normal

Zero

0/1

Infinity

0

0

0

1

0

Normal

Infinity

0/1

Zero

0

0

1

0

0

Normal

NaN

X

NaN

0

0

0

0

1

Denormal

Normal

0/1

Zero

0

0

1

0

0

Denormal

Denorma

l

0/1

NaN

0

0

0

0

1

Denormal

Zero

0/1

NaN

0

0

0

0

1

Denormal

Infinity

0/1

Zero

0

0

1

0

0

6-2

ALTFP_DIV Truth Table

UG-01058

2014.12.19

Altera Corporation

ALTFP_DIV IP Core