Numbers -6, Numbers – Altera Floating-Point User Manual

Page 30

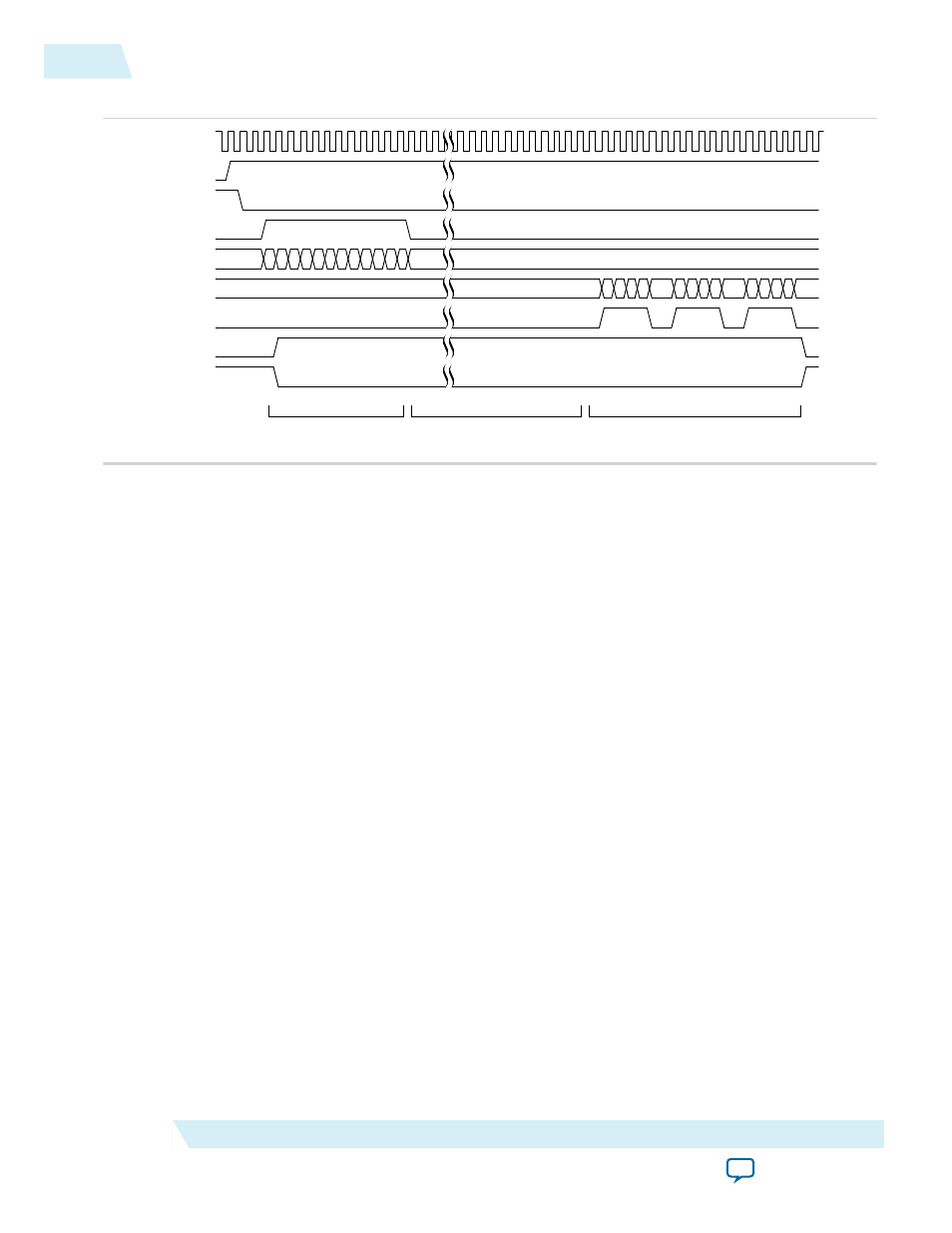

Figure 2-3: Matrix Inversion Timing Diagram

sysclk

enable

reset

load

datain

dataout

outvalid

busy

done

Loading Stage

Processing Stage

Output Stage

The following sequence describes the matrix inversion operation:

1. The operation begins when the

enable

signal is asserted and the

reset

signal is deasserted.

2. The

load

signal is asserted to load data from the

loaddata[]

port for the input matrix. As long as the

load

signal is high, data is loaded continuously for the input matrix.

3. The

busy

signal is asserted and the done signal is deasserted for a few clock cycles after the

datain[]

signal is asserted.

4. The

outvalid

signal is asserted multiple times to signify the availability of valid data on the

dataout[]

port. The number of times this signal is asserted equals the number of rows found in the output

matrix.

5. The

busy

and

done

signals are asserted when the last row of the output matrix has been burst out. This

assertion signifies the end of the matrix inversion operation on the first set of data.

ALTERA_FP_MATRIX_INV Design Example: Matrix Inverse of Single-

Precision Format Numbers

This design example uses the ALTERA_FP_MATRIX_INV IP core to show the matrix inversion

operation. The input matrix applied is an 8 × 8 matrix with a block size of 2. This example uses the

parameter editor GUI to define the core.

Related Information

•

Floating-Point IP Cores Design Example Files

on page 1-16

•

Provides the design example files for the Floating-Point IP cores

•

Provides information about installation, usage, and troubleshooting

2-6

ALTERA_FP_MATRIX_INV Design Example: Matrix Inverse of Single-Precision Format

Numbers

UG-01058

2014.12.19

Altera Corporation

ALTERA_FP_MATRIX_INV IP Core