Altera Floating-Point User Manual

Page 150

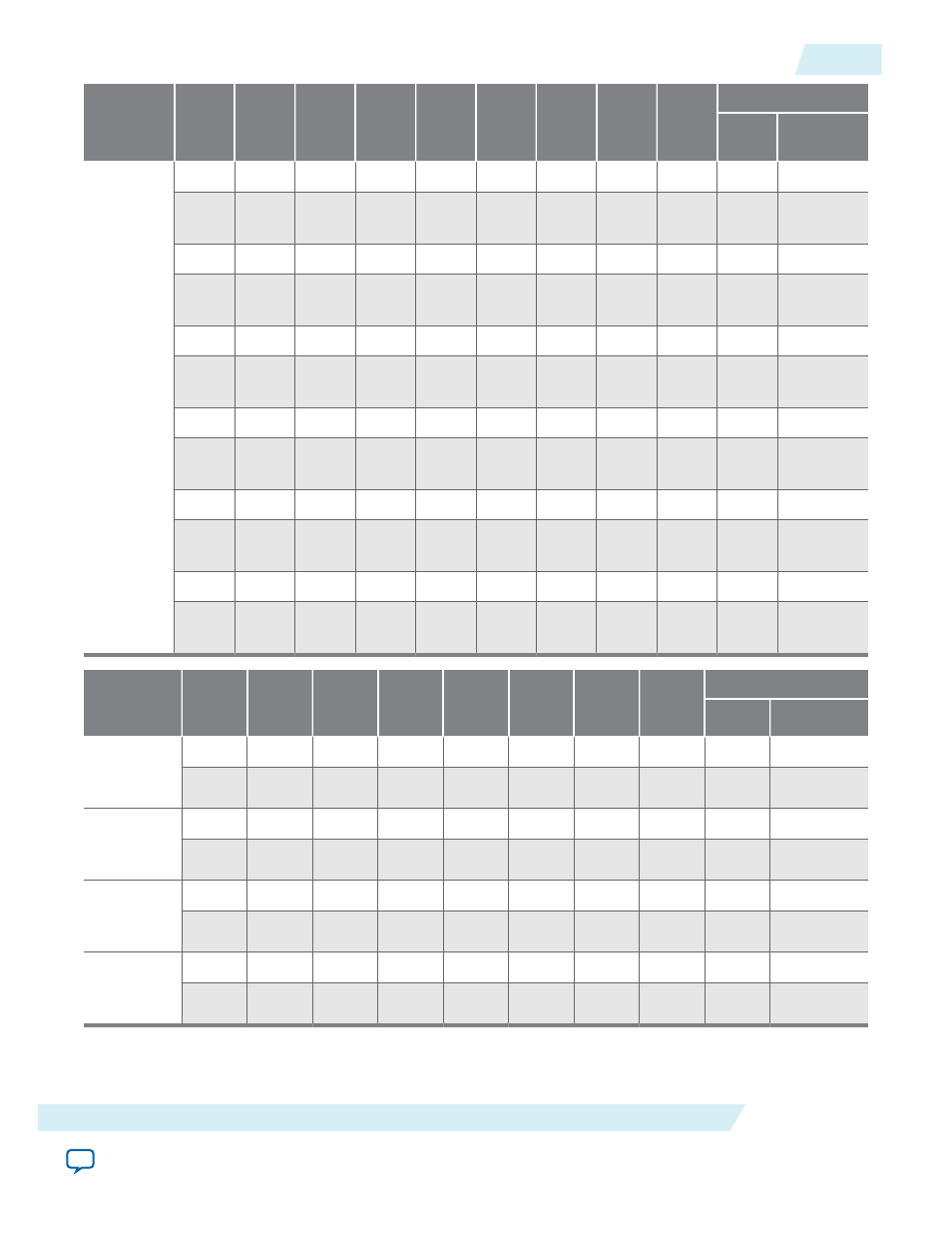

Family

Input

Width

Input

Fractio

n

Output

Precisi

on

Latenc

y

f

MAX

ALMs

M10K

M20K

DSP

Blocks

Logic Registers

Primar

y

Secondary

Arria 10

(10AX1

15H4F3

4I3SP)

32

0

Single

3

464.9

147

--

0

0

97

0

32

0

Doubl

e

2

458.93

161

--

0

0

72

0

32

16

Single

3

464.9

147

--

0

0

97

0

32

16

Doubl

e

2

432.15

160

--

0

0

72

0

32

32

Single

3

451.67

145

--

0

0

96

0

32

32

Doubl

e

2

419.99

154

--

0

0

72

0

64

0

Single

3

417.54

193

--

0

0

124

3

64

0

Doubl

e

3

407.33

305

--

0

0

193

3

64

16

Single

3

417.54

193

--

0

0

124

3

64

16

Doubl

e

3

407.33

305

--

0

0

193

3

64

32

Single

3

417.54

193

--

0

0

124

3

64

32

Doubl

e

3

407.33

305

--

0

0

193

3

Family

Input

Precisio

n

Output

Precisio

n

Latency

f

MAX

ALMs

M10K

M20K

DSP

Blocks

Logic Registers

Primary

Secondary

Arria V

(5AGXFB3H

4F40C5)

Single Double

2

371.61

93

0

—

0

71

0

Double Single

2

370.64

127

0

—

0

74

1

Cyclone V

(5CGXFC7D

6F31C7)

Single Double

2

346.14

93

0

—

0

72

1

Double Single

3

349.9

126

0

—

0

111

2

Stratix V

(5SGXEA7K

2F40C2)

Single Double

0

—

76

—

0

0

0

0

Double Single

0

717.36

126

—

0

0

34

0

Arria 10

(10AX115H4

F34I3SP)

Single Double

0

—

75

—

0

0

0

0

Double Single

0

—

126

—

0

0

34

0

UG-01058

2014.12.19

ALTERA_FP_FUNCTIONS Resource Utilization and Performance

18-23

ALTERA_FP_FUNCTIONS IP Core

Altera Corporation