Instantiating the megacore function in your design, Qsys design flow, Qsys design flow –4 – Altera Interlaken MegaCore Function User Manual

Page 16

2–4

Chapter 2: Getting Started

Qsys Design Flow

Interlaken MegaCore Function

June 2012

Altera Corporation

User Guide

You cannot simulate the Interlaken MegaCore function in the ModelSim-Altera

(ModelSim-AE) simulator. ModelSim-AE is the simulation tool provided with the

Quartus II software.

Instantiating the MegaCore Function in Your Design

After you generate your Interlaken MegaCore function variation, you can instantiate

it in the RTL for your design.

When you integrate your Interlaken MegaCore function variation in your design, note

the following connection and assignment requirements and recommendations:

■

If you turn off Exclude transceiver when you parameterize your Interlaken

MegaCore function, you must ensure that you connect the calibration clock

cal_blk_clk

to a clock signal with the appropriate frequency range of

10–125 MHz. The cal_blk_clk ports on other components that use the same

transceiver block must be connected to the same clock signal.

■

If you turn off Exclude transceiver when you parameterize your Interlaken

MegaCore function, you should set the RTL parameter SIM_FAST_RESET to 1 to

improve your transceiver simulation time. In this version of the Interlaken

MegaCore function, you must modify your RTL files to set the parameter. Add this

parameter to the parameter list in your HSIO bank instances with the value 1’b1.

The HSIO bank instances for the different variations are instantiations of the

modules alt_ntrlkn_hsio_bank_bpcs4, alt_ntrlkn_hsio_bank_10g,

alt_ntrlkn_hsio_bank_bpcs_3g

, or alt_ntrlkn_hsio_bank_pmad5.

Qsys Design Flow

You can use Qsys to build a system that contains your customized Interlaken

MegaCore function. You can easily add other components and quickly create a Qsys

system. Qsys can automatically generate HDL files that include all of the specified

components and interconnections. The HDL files are ready to be compiled by the

Quartus II software to produce output files for programming an Altera device.

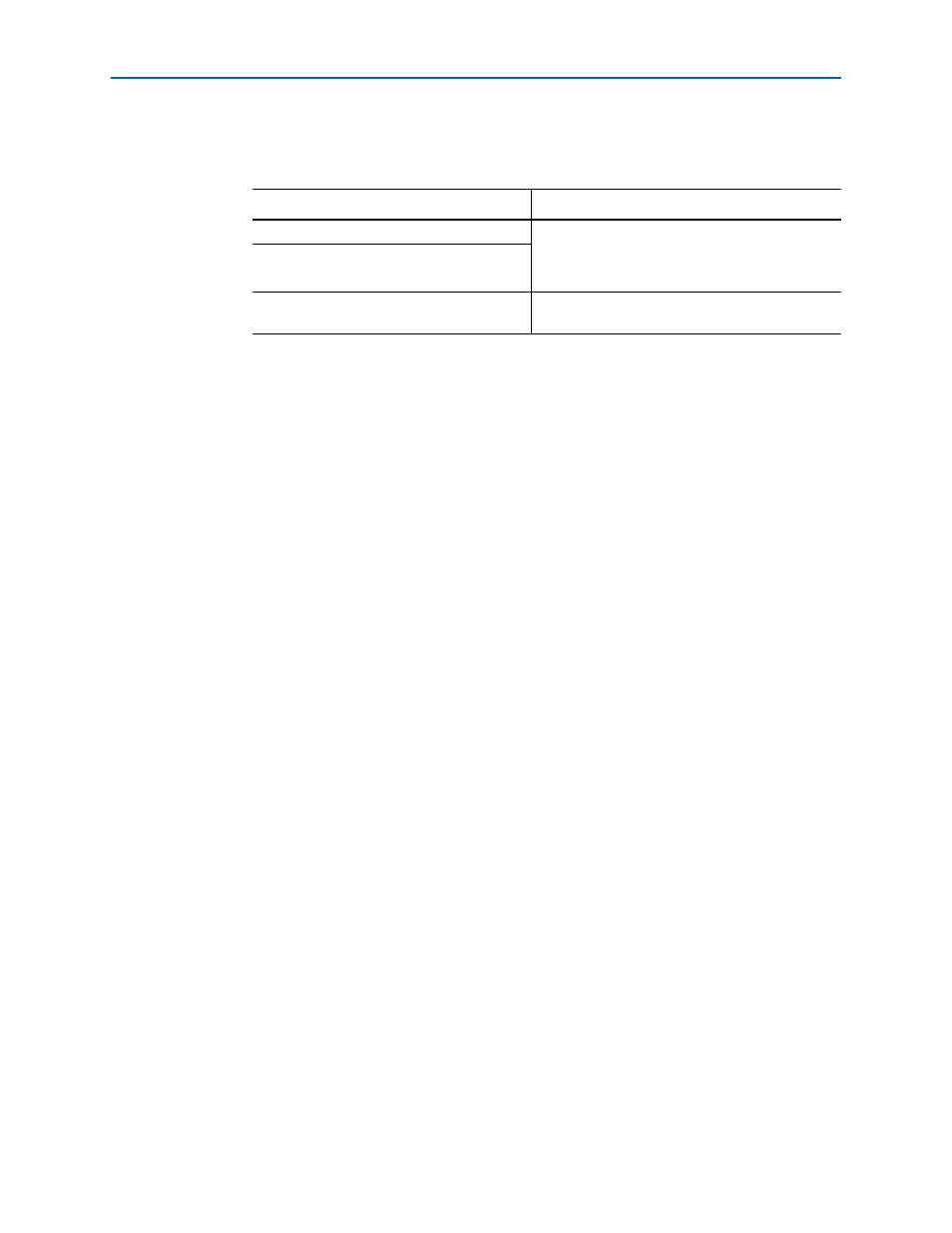

f

For Information About

Refer To

Quartus II software

See the Quartus II Help topics:

“About the Quartus II Software”

“About the MegaWizard Plug-In Manager”

MegaWizard Plug-In Manager

Functional simulation models for Altera IP

cores

chapter in volume 3 of

the Quartus II Handbook