Reset signals, Nction – Altera Interlaken MegaCore Function User Manual

Page 79

Appendix B: Excluding Transceivers for Faster Simulation

B–7

Reset in Interlaken MegaCore Functions Without Transceivers

June 2012

Altera Corporation

Interlaken MegaCore Function

User Guide

Reset Signals

In an Interlaken MegaCore function that excludes transceivers, the reset_export

signal is not available.

lists the individual reset signals that are available to

your testbench to reset the Interlaken MegaCore function, with their associated clock

domain.

To reset the Interlaken MegaCore function completely, you must assert all the reset

signals in

as described in

.

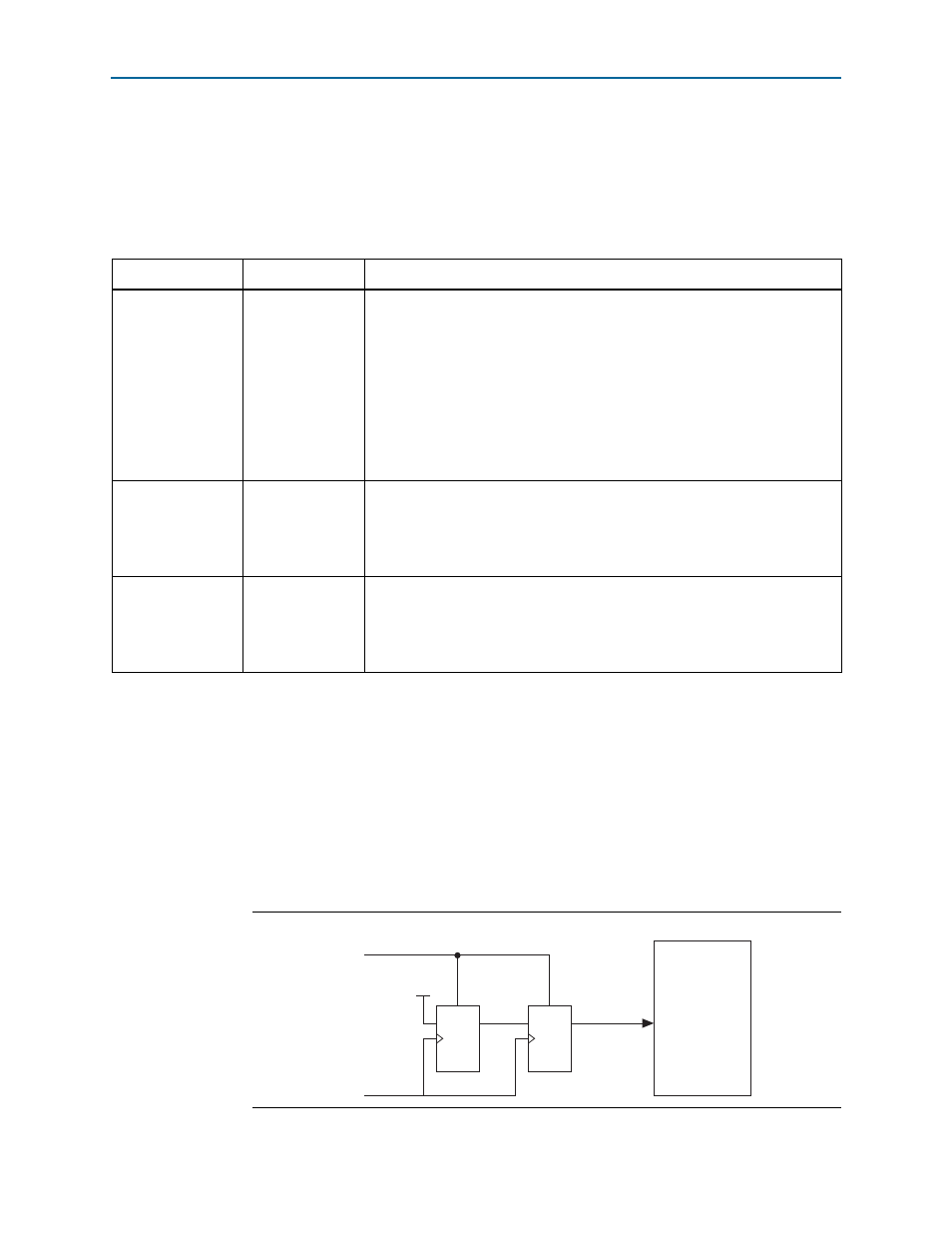

You can assert all the reset signals asynchronously to any clock. However, each reset

signal must be asserted for at least one full clock period of a specific clock, and be

deasserted synchronously to the rising edge of that clock. For example, the RX MAC

reset signal, rx_mac_r_reset, should be deasserted on the rising edge of

rx_mac_c_clk

. You must implement logic to ensure the minimal hold time and

synchronous deassertion of each reset input signal to the Interlaken MegaCore

function.

Figure B–5

shows a circuit that ensures these conditions for a reset signal.

Table B–2. Individual Reset Signals that Replace the reset_export Signal

Reset Signal

Clock Domain

Description

tx_lane_r_reset

tx_lane_c_clk

Asynchronous reset for the Interlaken MegaCore function PCS TX block.

Asserting this reset signal resets all the TX PCS internal registers, but does not

reset the TX FIFO pointers (which are in the TX MAC). Instead, it clears the

internal overflow bit, so the TX FIFO continues to empty, but deasserts the

internal FIFO write enable. You must hold this reset signal asserted for 256 clock

cycles to completely clear the TX FIFO.

This reset signal can be asserted asynchronously, but must stay asserted at

least one clock cycle and must be de-asserted synchronously with the rising

edge of tx_lane_c_clk. Refer to

Figure B–5

for a circuit that shows how to

enforce synchronous deassertion of tx_lane_r_reset.

rx_mac_r_reset

rx_mac_c_clk

Asynchronous reset for the Interlaken MegaCore function MAC RX block. This

reset signal can be asserted asynchronously, but must stay asserted at least one

clock cycle and must be de-asserted synchronously with rx_mac_c_clk. Refer

to

Figure B–5

for a circuit that shows how to enforce synchronous deassertion

of rx_mac_r_reset.

tx_mac_r_reset

tx_mac_c_clk

Asynchronous reset for the Interlaken MegaCore function MAC TX block. This

reset signal can be asserted asynchronously, but must stay asserted at least one

clock cycle and must be de-asserted synchronously with tx_mac_c_clk. Refer

to

Figure B–5

for a circuit that shows how to enforce synchronous deassertion

of tx_mac_r_reset.

Figure B–5. Circuit to Ensure Synchronous Deassertion of Asynchronous Reset Signal arst

D

D

Q

Q

arst

arst

V

CC

clk

arst

arst

Interlaken

MegaCore

Function